# Understanding Software Dynamics

Richard L. Sites

Foreword by Luiz André Barroso, Google Fellow

# Understanding Software Dynamics

Visit informit.com/series/professionalcomputing for a complete list of available publications.

The Pearson Addison-Wesley Professional Computing Series was created in 1990 to provide serious programmers and networking professionals with well-written and practical reference books. Pearson Addison-Wesley is renowned for publishing accurate and authoritative books on current and cutting-edge technology, and the titles in this series will help you understand the state of the art in programming languages, operating systems, and networks.

Make sure to connect with us! informit.com/socialconnect

# Understanding Software Dynamics

Richard L. Sites

## **♣**Addison-Wesley

Boston • Columbus • New York • San Francisco • Amsterdam • Cape Town

Dubai • London • Madrid • Milan • Munich • Paris • Montreal • Toronto • Delhi • Mexico City

São Paulo • Sydney • Hong Kong • Seoul • Singapore • Taipei • Tokyo

Many of the designations used by manufacturers and sellers to distinguish their products are claimed as trademarks. Where those designations appear in this book, and the publisher was aware of a trademark claim, the designations have been printed with initial capital letters or in all capitals.

The author and publisher have taken care in the preparation of this book, but make no expressed or implied warranty of any kind and assume no responsibility for errors or omissions. No liability is assumed for incidental or consequential damages in connection with or arising out of the use of the information or programs contained herein.

For information about buying this title in bulk quantities, or for special sales opportunities (which may include electronic versions; custom cover designs; and content particular to your business, training goals, marketing focus, or branding interests), please contact our corporate sales department at corpsales@pearsoned.com or (800) 382-3419.

For government sales inquiries, please contact governmentsales@pearsoned.com.

For questions about sales outside the U.S., please contact intlcs@pearson.com.

Visit us on the Web: informit.com/aw

Library of Congress Control Number: 2021944164

Copyright © 2022 Pearson Education, Inc.

Cover image: Art Heritage/Alamy Stock Photo

All rights reserved. This publication is protected by copyright, and permission must be obtained from the publisher prior to any prohibited reproduction, storage in a retrieval system, or transmission in any form or by any means, electronic, mechanical, photocopying, recording, or likewise. For information regarding permissions, request forms and the appropriate contacts within the Pearson Education Global Rights & Permissions Department, please visit www.pearson.com/permissions.

ISBN-13: 978-0-13-758973-9 ISBN-10: 0-13-758973-5

ScoutAutomatedPrintCode

Dedicated to the memory of Chuck Thacker, a true Friend of the Electron who could do more performance analysis in his head than most mortals.

## **Contents at a Glance**

| Forev<br>Prefa<br>Ackn | ents ix<br>word xix<br>ace xxi<br>owledgments xxv<br>at the Author xxvii |

|------------------------|--------------------------------------------------------------------------|

| Mea                    | surement 1                                                               |

| 1                      | My Program Is Too Slow 3                                                 |

| 2                      | Measuring CPUs 15                                                        |

| 3                      | Measuring Memory 31                                                      |

| 4                      | CPU and Memory Interaction 49                                            |

| 5                      | Measuring Disk/SSD 61                                                    |

| 6                      | Measuring Networks 85                                                    |

| 7                      | Disk and Network Database Interaction 111                                |

| 0bs                    | ervation 131                                                             |

| 8                      | Logging 133                                                              |

| 9                      | Aggregate Measures 141                                                   |

| 10                     | Dashboards 157                                                           |

| 11                     | Other Existing Tools 167                                                 |

| 12                     | Traces 193                                                               |

| 13                     | Observation Tool Design Principles 209                                   |

| Kernel-User Trace 217  |                                                                          |

| 14                     | KUtrace: Goals, Design, Implementation 219                               |

| 15                     | KUtrace: Linux Kernel Patches 227                                        |

| 16                     | KUtrace: Linux Loadable Module 239                                       |

| 17                     | KUtrace: User-Mode Runtime Control 245                                   |

| 18                     | KUtrace: Postprocessing 249                                              |

Ш

Ш

19 KUtrace: Display of Software Dynamics 257

#### IV Reasoning 267

- 20 What to Look For 269

- 21 Executing Too Much 271

- 22 Executing Slowly 279

- 23 Waiting for CPU 289

- 24 Waiting for Memory 299

- 25 Waiting for Disk 307

- 26 Waiting for Network 319

- 27 Waiting for Locks 337

- 28 Waiting for Time 357

- 29 Waiting for Queues 361

- 30 Recap 383

- A Sample Servers 387

- B Trace Entries 391

Glossary 397

References 405

Index 415

## **Contents**

|                     | 01160                                                            |  |  |  |

|---------------------|------------------------------------------------------------------|--|--|--|

|                     | Foreword xix                                                     |  |  |  |

|                     | Preface xxi                                                      |  |  |  |

| Acknowledgments xxv |                                                                  |  |  |  |

|                     | About the Author xxvii                                           |  |  |  |

|                     |                                                                  |  |  |  |

| Ме                  | asurement 1                                                      |  |  |  |

| 1                   | My Program Is Too Slow 3                                         |  |  |  |

|                     | 1.1 Datacenter Context 3                                         |  |  |  |

|                     | 1.2 Datacenter Hardware 5                                        |  |  |  |

|                     | 1.3 Datacenter Software 6                                        |  |  |  |

|                     | 1.4 Long-Tail Latency 7                                          |  |  |  |

|                     | 1.5 Thought Framework 9                                          |  |  |  |

|                     | 1.6 Order-of-Magnitude Estimates 9                               |  |  |  |

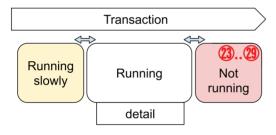

|                     | 1.7 Why Are Transactions Slow? 11                                |  |  |  |

|                     | 1.8 The Five Fundamental Resources 12                            |  |  |  |

|                     | 1.9 Summary 12                                                   |  |  |  |

| 2                   | Measuring CPUs 15                                                |  |  |  |

|                     | 2.1 How We Got Here 15                                           |  |  |  |

|                     | 2.2 Where Are We Now? 19                                         |  |  |  |

|                     | 2.3 Measuring the Latency of an add Instruction 20               |  |  |  |

|                     | 2.4 Straight-Line Code Fail 21                                   |  |  |  |

|                     | 2.5 Simple Loop, Loop Overhead Fail, Optimizing Compiler Fail 21 |  |  |  |

|                     | 2.6 Dead Variable Fail 24                                        |  |  |  |

|                     | 2.7 Better Loop 25                                               |  |  |  |

|                     | 2.8 Dependent Variables 26                                       |  |  |  |

|                     | 2.9 Actual Execution Latency 26                                  |  |  |  |

|                     | 2.10 More Nuance 27                                              |  |  |  |

|                     | 2.11 Summary 28                                                  |  |  |  |

|                     | Exercises 28                                                     |  |  |  |

| 3                   | Measuring Memory 31                                              |  |  |  |

|                     | 3.1 Memory Timing 31                                             |  |  |  |

|                     | 3.2 About Memory 32                                              |  |  |  |

|                     | 3.3 Cache Organization 34                                        |  |  |  |

|                     | 3.4 Data Alignment 36                                            |  |  |  |

3.5 Translation Lookaside Buffer Organization 36

| 3.6 | The Measurements 37       |    |

|-----|---------------------------|----|

| 3.7 | Measuring Cache Line Size | 38 |

| 3.8 | Problem: N+1 Prefetching  | 10 |

- 3.9 Dependent Loads 41

- 3.10 Non-random Dynamic Random-Access Memory 42

- 3.11 Measuring Total Size of Each Cache Level 43

- 3.12 Measuring Cache Associativity of Each Level 45

- 3.13 Translation Buffer Time 46

- 3.14 Cache Underutilization 46

- 3.15 Summary 46

Exercises 47

#### 4 CPU and Memory Interaction 49

- 4.1 Cache Interaction 49

- 4.2 Simple Matrix Multiply Dynamics 51

- 4.3 Estimates 51

- 4.4 Initialization, Cross-Checking, and Observing 52

- 4.5 Initial Results 53

- 4.6 Faster Matrix Multiply, Transpose Method 55

- 4.7 Faster Matrix Multiply, Subblock Method 57

- 4.8 Cache-Aware Computation 58

- 4.9 Summary 58

Exercises 59

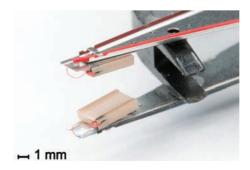

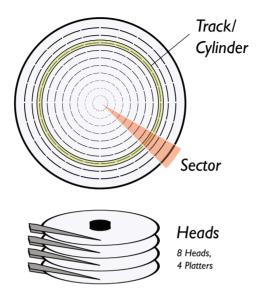

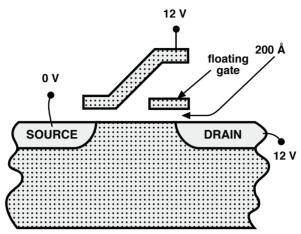

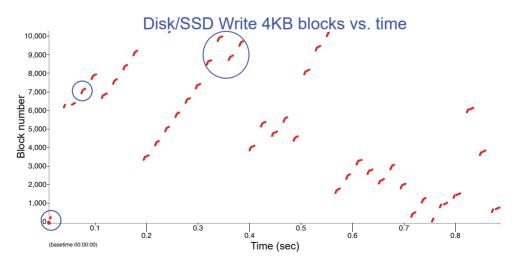

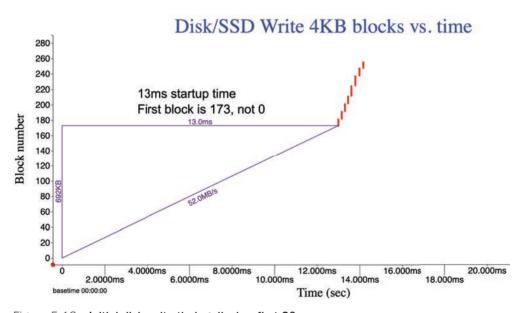

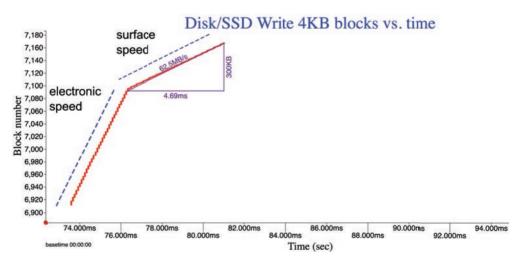

#### 5 Measuring Disk/SSD 61

- 5.1 About Hard Disks 62

- 5.2 About SSDs 64

- 5.3 Software Disk Access and On-Disk Buffering 66

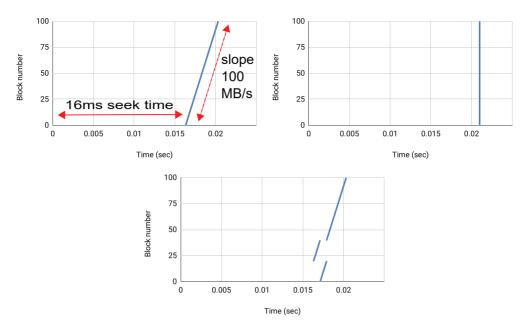

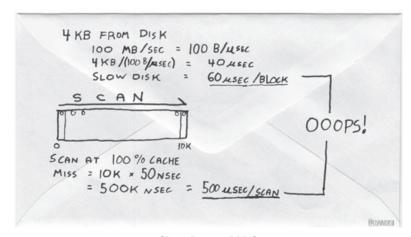

- 5.4 How Fast Is a Disk Read? 68

- 5.5 A Little Back-of-the-Envelope Calculation 71

- 5.6 How Fast Is a Disk Write? 72

- 5.7 Results 73

- 5.8 Reading from Disk 73

- 5.9 Writing to Disk 77

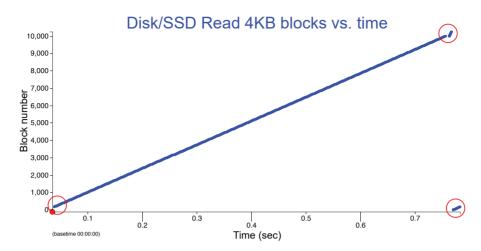

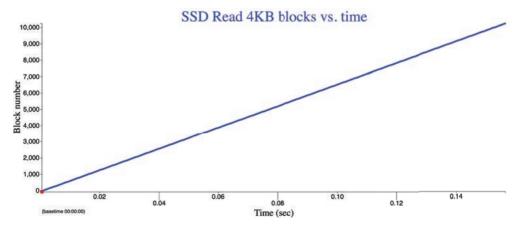

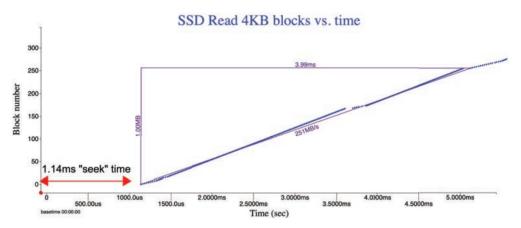

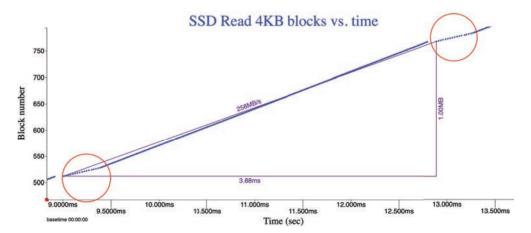

- 5.10 Reading from SSD 80

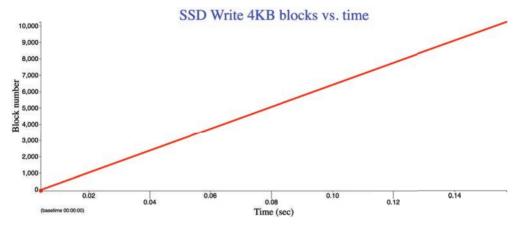

- 5.11 Writing to SSD 82

- 5.12 Multiple Transfers 82

- 5.13 Summary 83

Exercises 84

#### 6 Measuring Networks 85

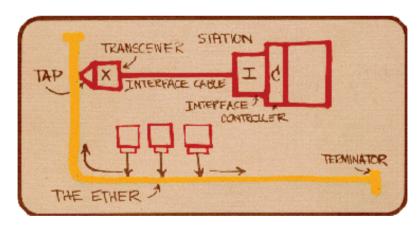

- 6.1 About Ethernet 87

- 6.2 About Hubs, Switches, and Routers 89

- 6.3 About TCP/IP 89

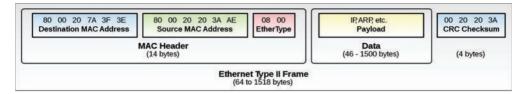

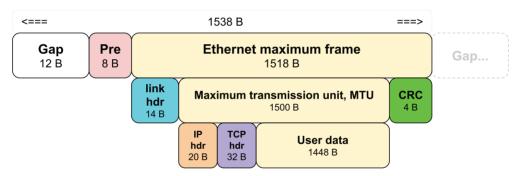

- 6.4 About Packets 90

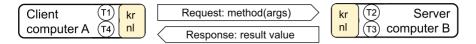

- 6.5 About Remote Procedure Calls (RPCs) 91

- 6.6 Slop 93

- 6.7 Observing Network Traffic 94

- 6.8 Sample RPC Message Definition 96

- 6.9 Sample Logging Design 99

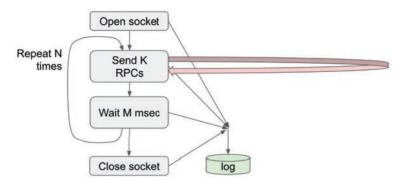

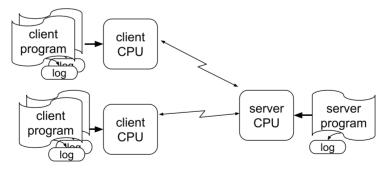

- 6.10 Sample Client-Server System Using RPCs 100

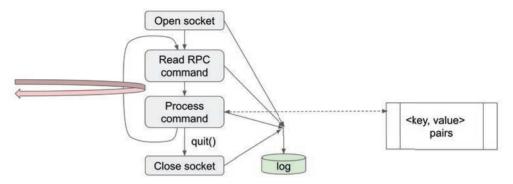

- 6.11 Sample Server Program 101

- 6.12 Spinlocks 101

- 6.13 Sample Client Program 102

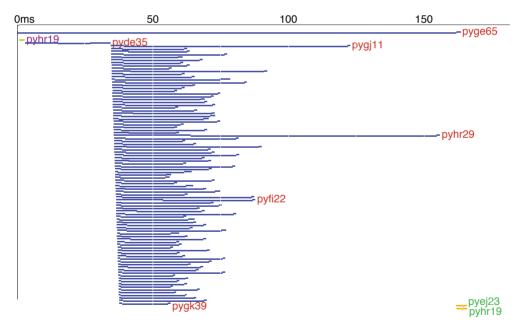

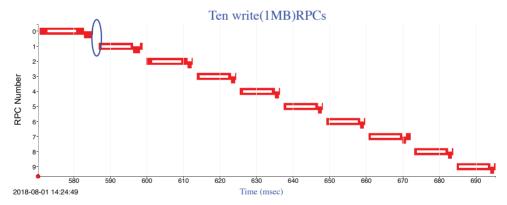

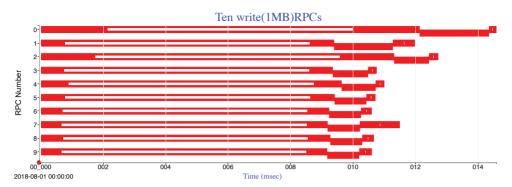

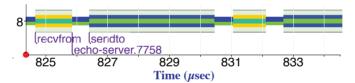

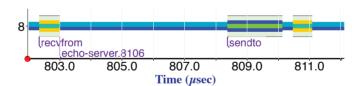

- 6.14 Measuring One Sample Client-Server RPC 105

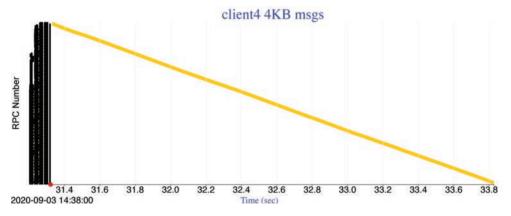

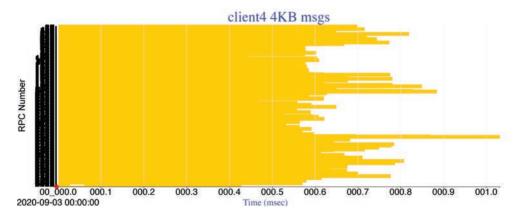

- 6.15 Postprocessing RPC Logs 106

- 6.16 Observations 107

- 6.17 Summary 108

Exercises 109

#### 7 Disk and Network Database Interaction 111

- 7.1 Time Alignment 111

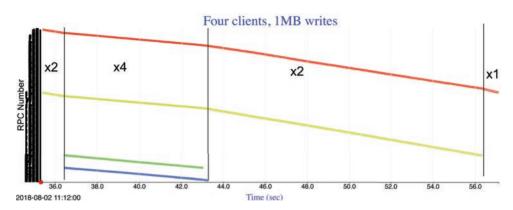

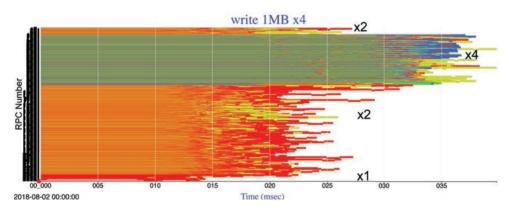

- 7.2 Multiple Clients 117

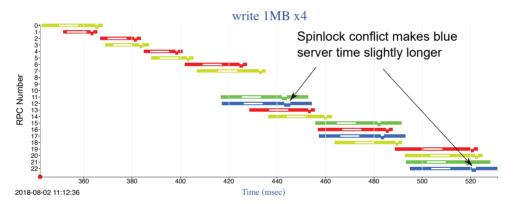

- 7.3 Spinlocks 118

- 7.4 Experiment 1 118

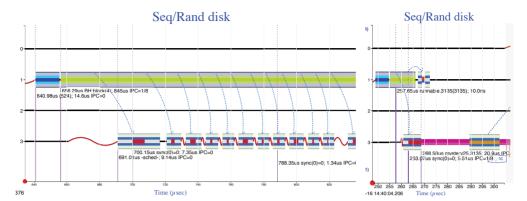

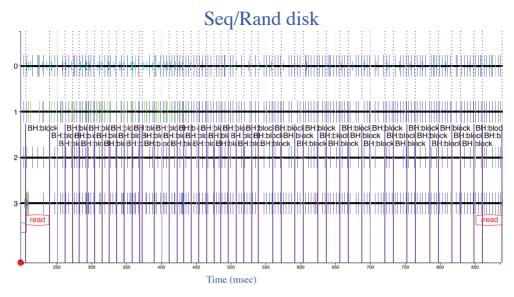

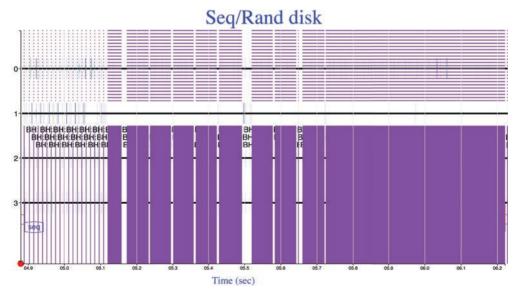

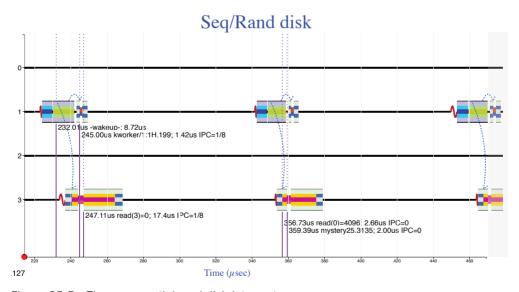

- 7.5 On-Disk Database 121

- 7.6 Experiment 2 121

- 7.7 Experiment 3 125

- 7.8 Logging 127

- 7.9 Understanding Transaction Latency Variation 128

- 7.10 Summary 128

Exercises 129

#### II Observation 131

#### 8 Logging 133

- 8.1 Observation Tools 133

- 8.2 Logging 133

- 8.3 Basic Logging 134

- 8.4 Extended Logging 135

- 8.5 Timestamps 135

- 8.6 RPC IDs 136

- 8.7 Log File Formats 137

- 8.8 Managing Log Files 138

- 8.9 Summary 139

#### 9 Aggregate Measures 141

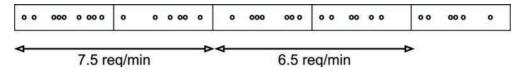

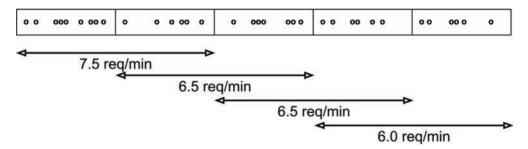

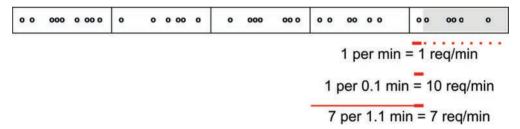

- 9.1 Uniform vs. Bursty Event Rates 142

- 9.2 Measurement Intervals 143

- 9.3 Timelines 143

- 9.4 Further Summarizing of Timelines 145

- 9.5 Histogram Time Scales 147

- 9.6 Aggregating Per-Event Measurements 150

- 9.7 Patterns of Values Over Time 151

- 9.8 Update Intervals 152

- 9.9 Example Transactions 154

- 9.10 Conclusion 155

#### 10 Dashboards 157

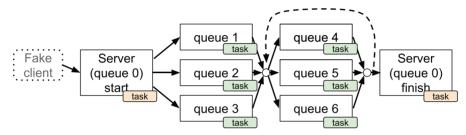

- 10.1 Sample Service 157

- 10.2 Sample Dashboards 159

- 10.3 Master Dashboard 159

- 10.4 Per-Instance Dashboards 163

- 10.5 Per-Server Dashboards 164

- 10.6 Sanity Checks 164

- 10.7 Summary 165

- Exercises 165

#### 11 Other Existing Tools 167

- 11.1 Kinds of Observation Tools 167

- 11.2 Data to Observe 169

- 11.3 top Command 170

- 11.4 /proc and /sys Pseudofiles 171

- 11.5 time Command 171

- 11.6 perf Command 171

- 11.7 oprofile, CPU Profiler 173

- 11.8 strace, System Calls 176

- 11.9 ltrace, CPU C Library Calls 179

|   |     | 11.10  | ftrace, CPU Trace 180                                     |  |

|---|-----|--------|-----------------------------------------------------------|--|

|   |     | 11.11  | mtrace, Memory Malloc/Free 183                            |  |

|   |     | 11.12  | blktrace, Disk Trace 184                                  |  |

|   |     | 11.13  | tcpdump and Wireshark, Network Trace 187                  |  |

|   |     | 11.14  | locktrace, Critical Section Locks 189                     |  |

|   |     | 11.15  | Offered Load, Outbound Calls, and Transaction Latency 189 |  |

|   |     | 11.16  | Summary 191                                               |  |

|   |     | Exerci | ses 191                                                   |  |

|   | 12  | Traces | s 193                                                     |  |

|   |     | 12.1   | Tracing Advantages 193                                    |  |

|   |     | 12.2   | Tracing Disadvantages 194                                 |  |

|   |     | 12.3   | The Three Starting Questions 194                          |  |

|   |     | 12.4   | Example: Early Program Counter Trace 197                  |  |

|   |     | 12.5   | Example: Per-Function Counts and Time 199                 |  |

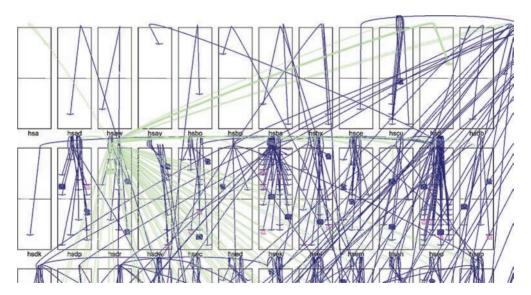

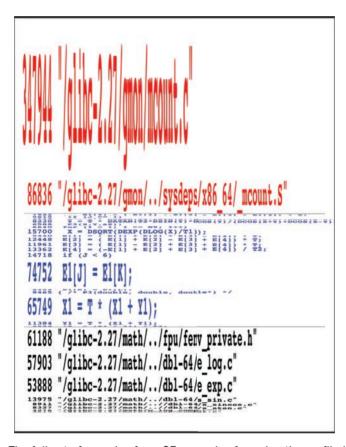

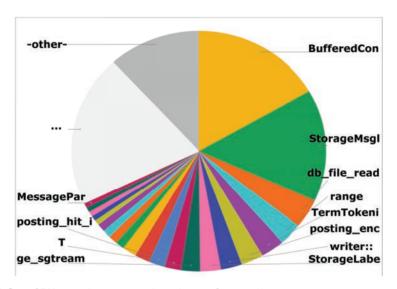

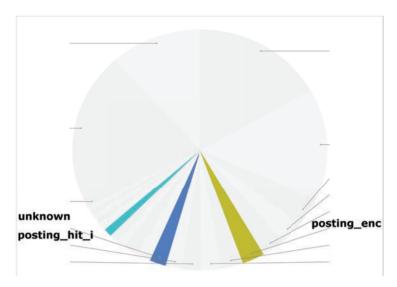

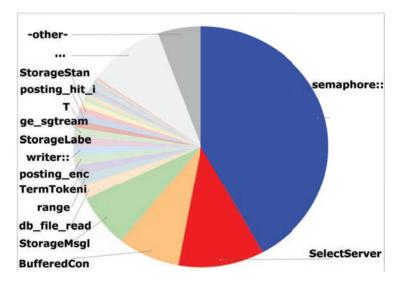

|   |     | 12.6   | Case Study: Per-Function Trace of Gmail 203               |  |

|   |     | 12.7   | Summary 207                                               |  |

|   | 13  | Obser  | vation Tool Design Principles 209                         |  |

|   |     | 13.1   | What to Observe 209                                       |  |

|   |     | 13.2   | How Frequently and For How Long? 210                      |  |

|   |     | 13.3   | How Much Overhead? 211                                    |  |

|   |     | 13.4   | Design Consequences 212                                   |  |

|   |     | 13.5   | Case Study: Histogram Buckets 212                         |  |

|   |     | 13.6   | Designing Data Display 214                                |  |

|   |     | 13.7   | Summary 215                                               |  |

|   |     |        |                                                           |  |

| Ш | Ker | nel-Us | er Trace 217                                              |  |

|   | 14  | KUtra  | ce: Goals, Design, Implementation 219                     |  |

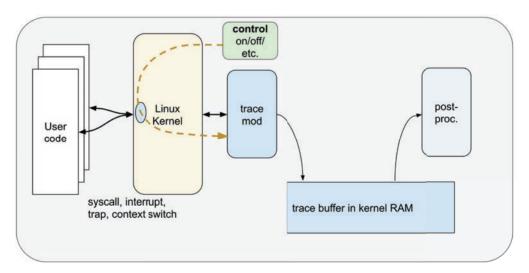

|   |     | 14.1   | Overview 219                                              |  |

|   |     | 14.2   | Goals 220                                                 |  |

|   |     | 14.3   | Design 221                                                |  |

|   |     | 14.4   | Implementation 223                                        |  |

|   |     | 14.5   | Kernel Patches and Module 224                             |  |

|   |     | 14.6   | Control Program 224                                       |  |

|   |     | 14.7   | Postprocessing 225                                        |  |

|   |     | 14.8   | A Note on Security 225                                    |  |

|   |     | 14.9   | Summary 225                                               |  |

| 15 | KUtrac  | e: Linux Kernel Patches 227                                                              |

|----|---------|------------------------------------------------------------------------------------------|

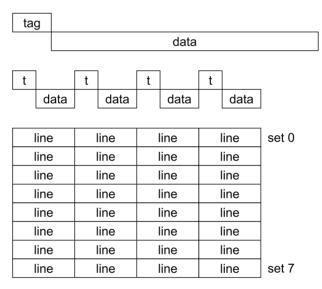

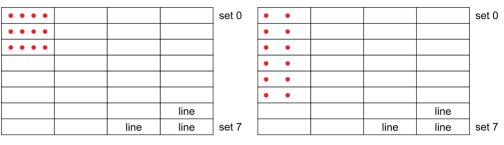

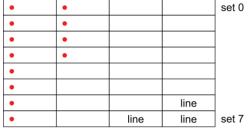

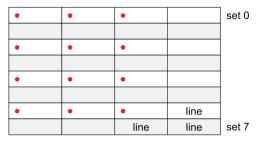

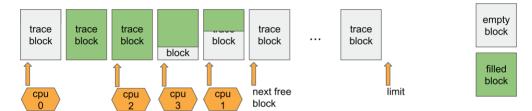

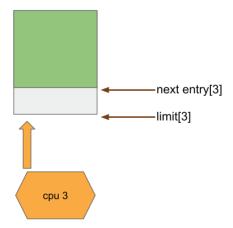

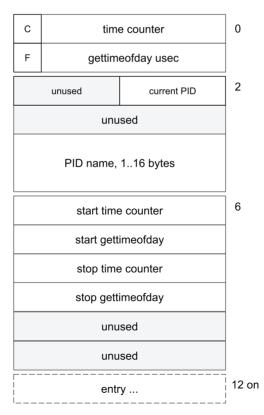

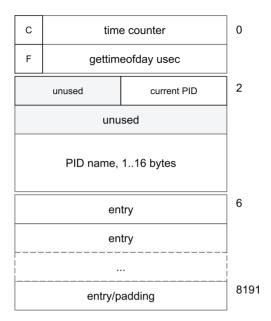

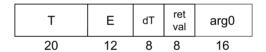

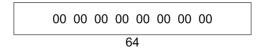

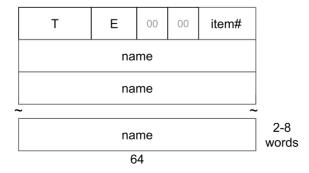

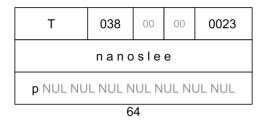

|    | 15.1    | Trace Buffer Data Structures 228                                                         |

|    | 15.2    | Raw Traceblock Format 229                                                                |

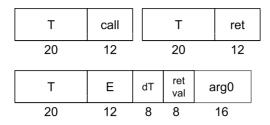

|    | 15.3    | Trace Entries 230                                                                        |

|    | 15.4    | IPC Trace Entries 232                                                                    |

|    | 15.5    | Timestamps 233                                                                           |

|    | 15.6    | Event Numbers 233                                                                        |

|    | 15.7    | Nested Trace Entries 233                                                                 |

|    | 15.8    | Code 234                                                                                 |

|    | 15.9    | Packet Tracing 234                                                                       |

|    | 15.10   | AMD/Intel x86-64 Patches 236                                                             |

|    | 15.11   | Summary 237                                                                              |

|    | Exercis | es 237                                                                                   |

| 16 | KUtrac  | e: Linux Loadable Module 239                                                             |

|    | 16.1    | Kernel Interface Data Structures 239                                                     |

|    |         | Module Load/Unload 240                                                                   |

|    |         | Initializing and Controlling Tracing 241                                                 |

|    |         | Implementing Trace Calls 241                                                             |

|    |         | Insert1 241                                                                              |

|    |         | InsertN 243                                                                              |

|    |         | Switching to a New Traceblock 244                                                        |

|    |         | Summary 244                                                                              |

| 47 |         | ,                                                                                        |

| 17 |         | e: User-Mode Runtime Control 245                                                         |

|    |         | Controlling Tracing 245                                                                  |

|    |         | Standalone kutrace_control Program 246                                                   |

|    |         | The Underlying kutrace_lib Library 246  The Control Interface to the Leadable Medule 247 |

|    |         | The Control Interface to the Loadable Module 247                                         |

|    | 17.5    | Summary 247                                                                              |

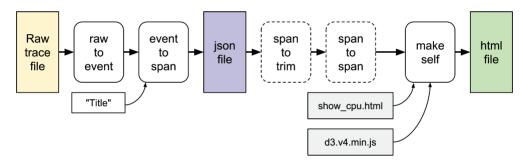

| 18 | KUtrac  | e: Postprocessing 249                                                                    |

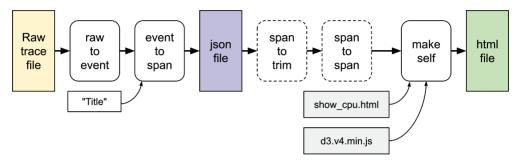

|    | 18.1    | Postprocessing Details 249                                                               |

|    | 18.2    | The rawtoevent Program 250                                                               |

|    | 18.3    | The eventtospan Program 251                                                              |

|    | 18.4    | The spantotrim Program 253                                                               |

|    | 18.5    | The spantospan Program 253                                                               |

|    | 18.6    | The samptoname_k and samptoname_u Programs 253                                           |

18.7 The makeself Program 254

- 18.8 KUtrace JSON Format 254

- 18.9 Summary 256

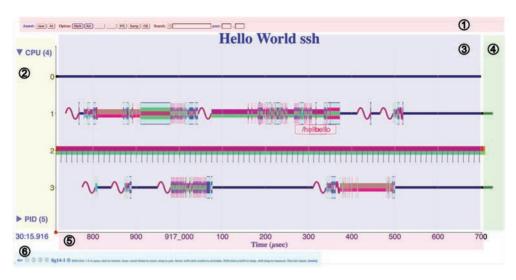

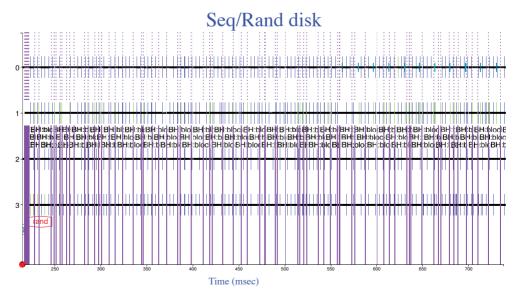

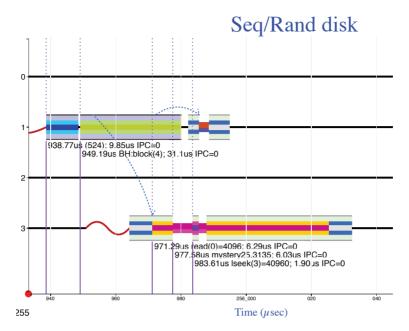

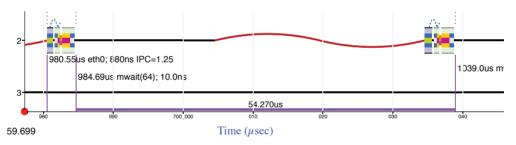

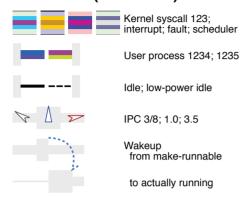

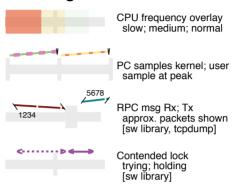

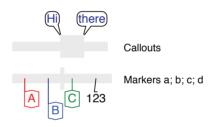

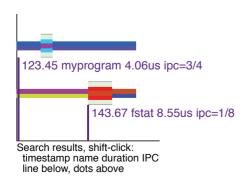

#### 19 KUtrace: Display of Software Dynamics 257

- 19.1 Overview 257

- 19.2 Region 1, Controls 258

- 19.3 Region 2, Y-axis 259

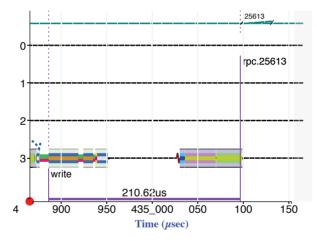

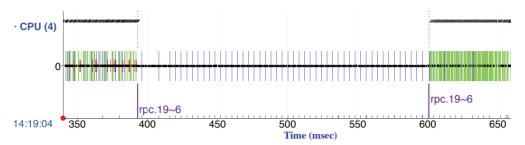

- 19.4 Region 3, Timelines 260

- 19.5 Region 4, IPC Legend 265

- 19.6 Region 5, X-axis 265

- 19.7 Region 6, Save/Restore 265

- 19.8 Secondary Controls 265

- 19.9 Summary 266

#### IV Reasoning 267

#### 20 What to Look For 269

20.1 Overview 269

#### 21 Executing Too Much 271

- 21.1 Overview 271

- 21.2 The Program 271

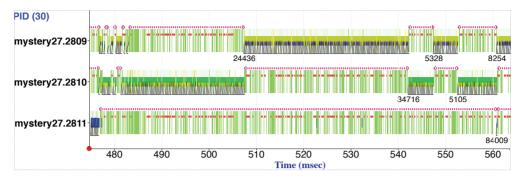

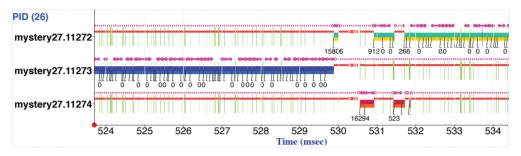

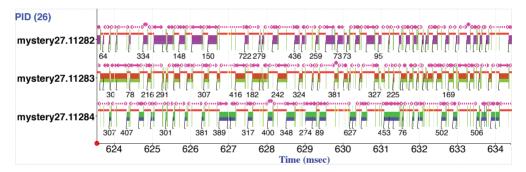

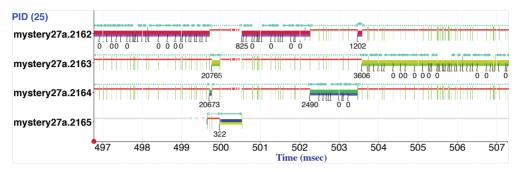

- 21.3 The Mystery 272

- 21.4 Exploring and Reasoning 273

- 21.5 Mystery Understood 277

- 21.6 Summary 277

#### 22 Executing Slowly 279

- 22.1 Overview 279

- 22.2 The Program 279

- 22.3 The Mystery 280

- 22.4 Floating-Point Antagonist 282

- 22.5 Memory Antagonist 285

- 22.6 Mystery Understood 286

- 22.7 Summary 286

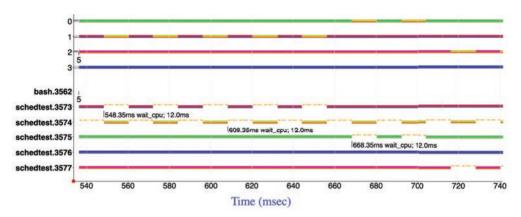

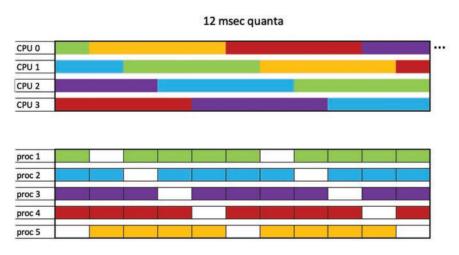

#### 23 Waiting for CPU 289

- 23.1 The Program 289

- 23.2 The Mystery 289

- 23.3 Exploring and Reasoning 290

- 23.4 Mystery 2 292

26.8

26.9

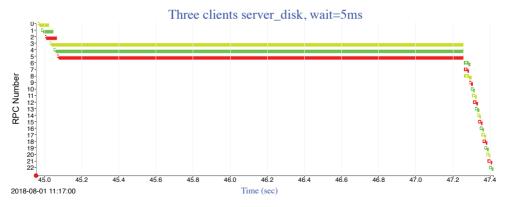

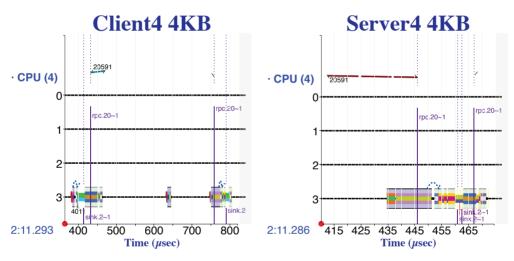

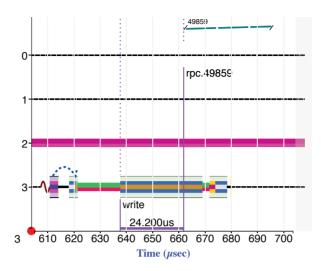

Experiment 3 329

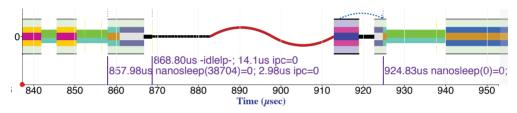

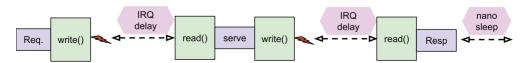

Experiment 4 330 26.10 Mysteries Understood 333

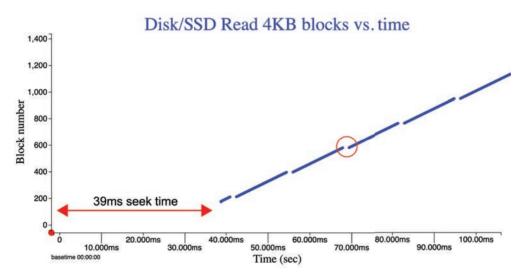

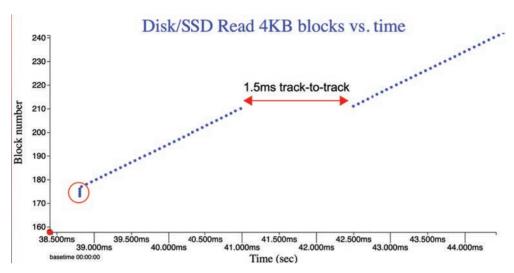

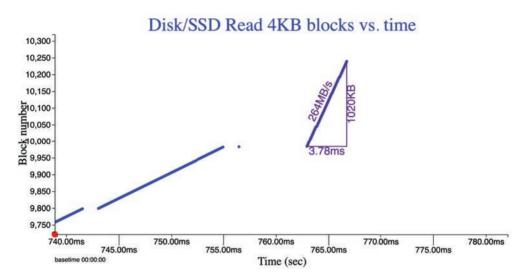

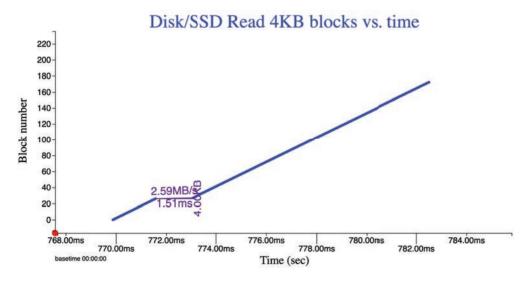

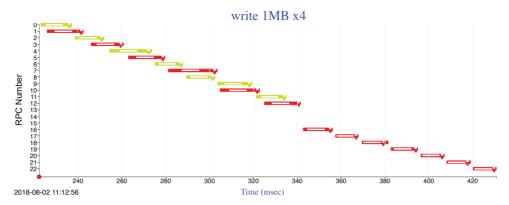

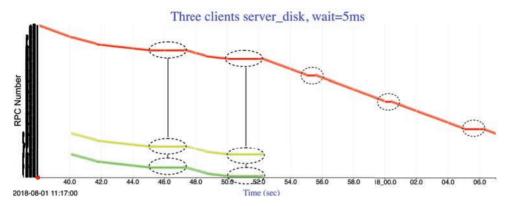

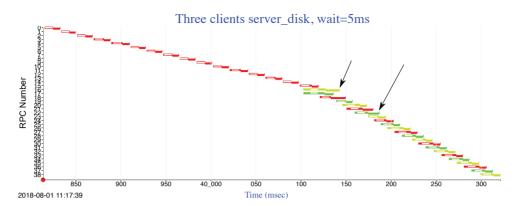

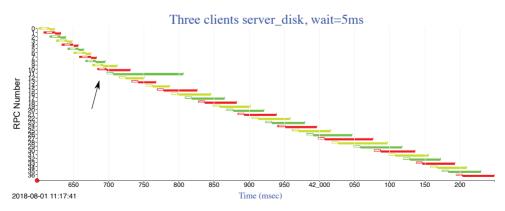

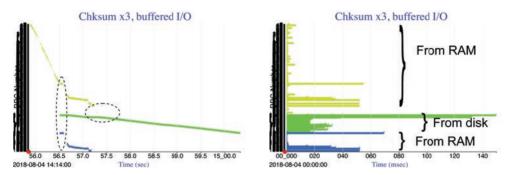

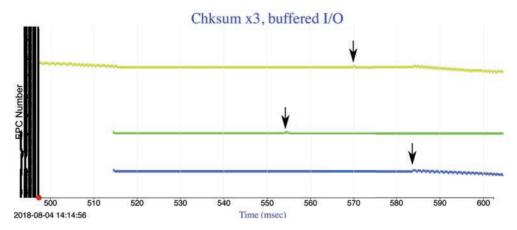

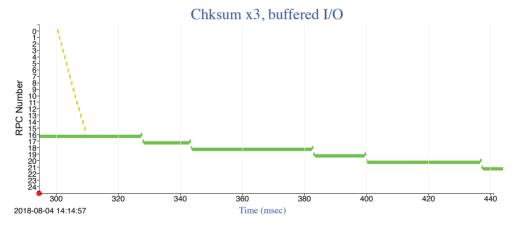

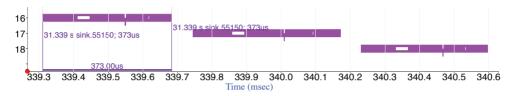

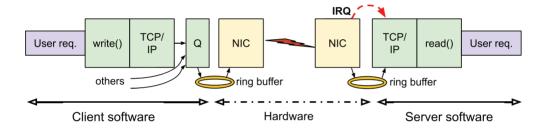

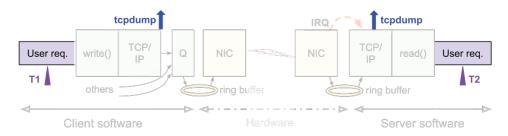

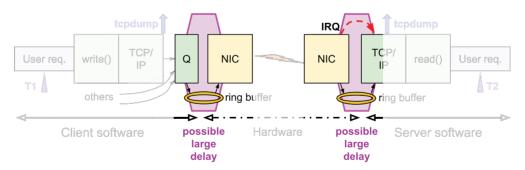

23.5 Mystery 2 Understood 293 23.6 Bonus Mystery 295 23.7 Summary 297 297 Exercises 24 Waiting for Memory 299 24.1 The Program 299 24.2 The Mystery 300 24.3 Exploring and Reasoning 300 24.4 Mystery 2: Access to a Page Table 304 24.5 Mystery 2 Understood 304 24.6 Summary 306 Exercises 306 25 Waiting for Disk 307 25.1 The Program 307 25.2 The Mystery 307 25.3 Exploring and Reasoning 308 25.4 Reading 40MB 310 25.5 Reading Sequential 4KB Blocks 311 25.6 Reading Random 4KB Blocks 313 25.7 Writing and Sync of 40MB on SSD 314 25.8 Reading 40MB on SSD 315 25.9 Two Programs Accessing Two Files at Once 316 25.10 Mysteries Understood 317 25.11 Summary 317 Exercises 317 26 Waiting for Network 319 26.1 Overview 319 26.2 The Programs 320 26.3 Experiment 1 321 26.4 Experiment 1 Mystery 322 26.5 Experiment 1 Exploring and Reasoning 323 26.6 Experiment 1 What About the Time Between RPCs? 327 26.7 Experiment 2 329

|    | 26.11   | Bonus Anomaly 334                                              |

|----|---------|----------------------------------------------------------------|

|    | 26.12   | Summary 336                                                    |

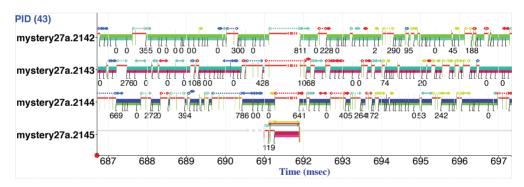

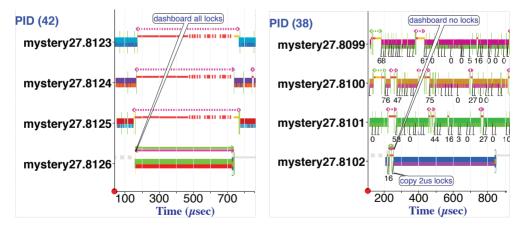

| 27 | Waiting | g for Locks 337                                                |

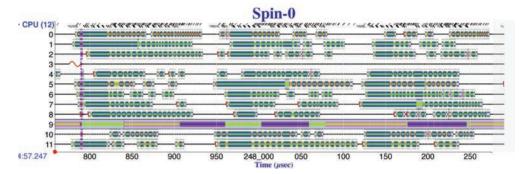

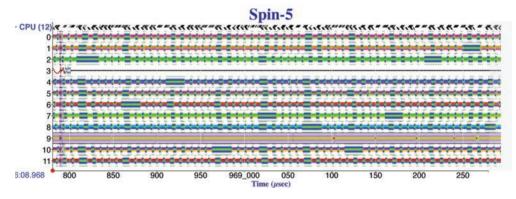

|    | 27.1    | Overview 337                                                   |

|    | 27.2    | The Program 341                                                |

|    | 27.3    | Experiment 1: Long Lock Hold Times 344                         |

|    |         | 27.3.1 Simple Locking 344                                      |

|    |         | 27.3.2 Lock Saturation 345                                     |

|    | 27.4    | Mysteries in Experiment 1 345                                  |

|    | 27.5    | Exploring and Reasoning in Experiment 1 346                    |

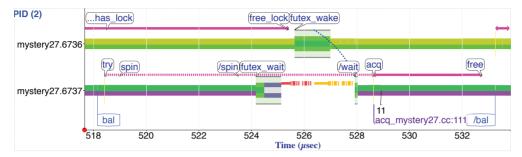

|    |         | 27.5.1 Lock Capture 347                                        |

|    |         | 27.5.2 Lock Starvation 348                                     |

|    | 27.6    | Experiment 2: Fixing Lock Capture 348                          |

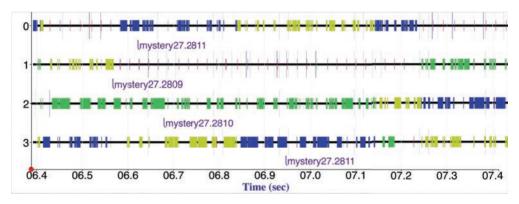

|    | 27.7    | Experiment 3: Fixing Lock Contention via Multiple Locks 349    |

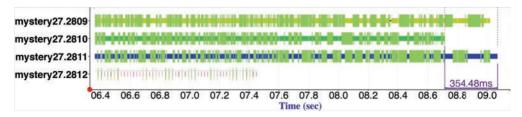

|    | 27.8    | Experiment 4: Fixing Lock Contention via Less Locked Work 351  |

|    | 27.9    | Experiment 5: Fixing Lock Contention via RCU for Dashboard 353 |

|    | 27.10   | Summary 355                                                    |

| 28 | Waiting | g for Time 357                                                 |

|    | 28.1    | Periodic Work 357                                              |

|    | 28.2    | Timeouts 358                                                   |

|    | 28.3    | Timeslicing 358                                                |

|    | 28.4    | Inline Execution Delays 359                                    |

|    | 28.5    | Summary 359                                                    |

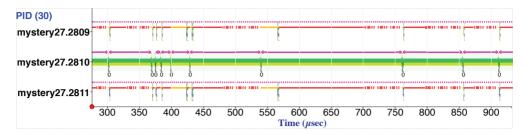

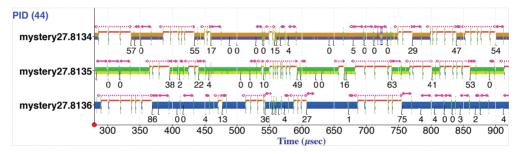

| 29 | Waiting | g for Queues 361                                               |

|    | 29.1    | Overview 361                                                   |

|    | 29.2    | Request Distribution 363                                       |

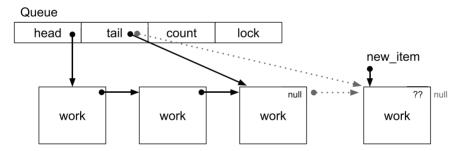

|    | 29.3    | Queue Structure 364                                            |

|    | 29.4    | Worker Tasks 365                                               |

|    | 29.5    | Primary Task 365                                               |

|    | 29.6    | Dequeue 365                                                    |

The "Work" Routine 367

Enqueue 366

Spinlock 366

29.10 Simple Examples 367

29.7

29.8

29.9

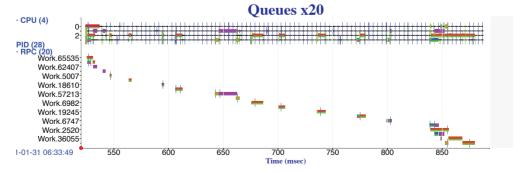

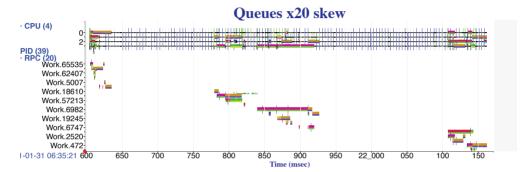

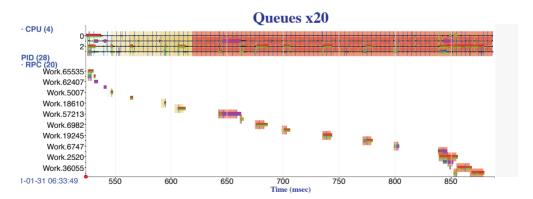

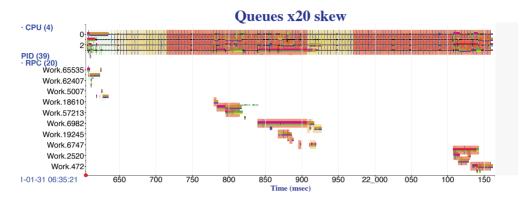

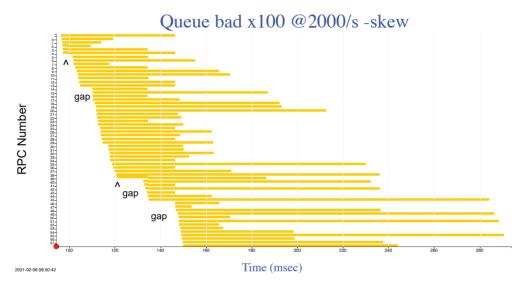

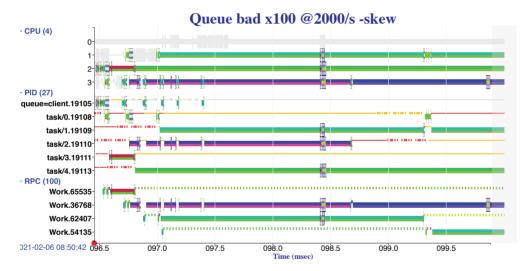

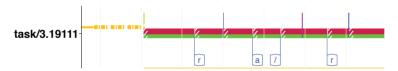

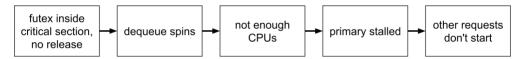

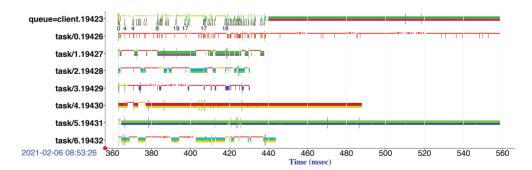

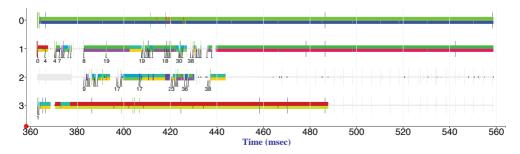

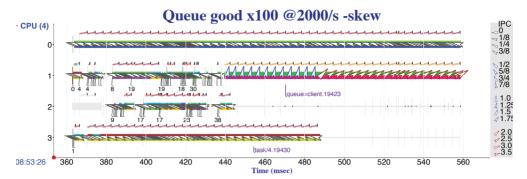

29.11 What Could Possibly Go Wrong? 368 29.12 CPU Frequency 369 29.13 Complex Examples 370 29.14 Waiting for CPUs: RPC Log 370 29.15 Waiting for CPUs: KUtrace 371 29.16 PlainSpinLock Flaw 374 29.17 Root Cause 375 29.18 PlainSpinLock Fixed: Observability 376 29.19 Load Balancing 377 29.20 Queue Depth: Observability 378 29.21 Spin at the End 378 29.22 One More Flaw 379 29.23 Cross-Checking 379 29.24 Summary 380 Exercises 380 30 Recap 383 30.1 What You Learned 383 30.2 What We Haven't Covered 385 30.3 Next Steps 385 30.4 Summary (for the Entire Book) 386

#### A Sample Servers 387

- A.1 Sample Server Hardware 387

- A.2 Connecting the Servers 388

#### B Trace Entries 391

- B.1 Fixed-Length Trace Entries 391

- B.2 Variable-Length Trace Entries 392

- B.3 Event Numbers 393

- B.3.1 Events Inserted by Kernel-Mode KUtrace Patches 394

- B.3.2 Events Inserted by User-Mode Code 395

- B.3.3 Events Inserted by Postprocessing Code 395

#### Glossary 397

References 405

Index 415

#### **Foreword**

Dick Sites approaches problem-solving in a way that is shockingly rare these days: he finds it almost personally offensive to make guesses, and instead he insists on understanding a phenomenon before trying to fix it. When faced with the complexity of modern computer systems, including their hardware and software, most programmers approach performance debugging armed with a hunch about what is happening and proceed to "try this, try that" with the hope that this might yield a shortcut to a solution. Those of us who use this method are implicitly giving up on the possibility of truly grasping the complex interactions that could cause a program to underperform. The idea that something computer related is beyond understanding certainly doesn't occur to Dick. Often it is the case that basic tools that provide telemetry on a program's behavior are missing. In those cases Dick does the obvious thing (for Dick), which is to build them, including the visualization framework that compresses essential information about program execution into readable charts that shine a bright light into program dynamics.

When you go through Dick's remarkable career, it becomes clear why he is confident in his ability to understand complex computing systems. He became a programmer at age 10 in 1959, and his curiosity about computing resulted in a career where he studied or worked closely with giants of our field such as Fran Allen, Fred Brooks, John Cocke, Don Knuth, and Chuck Seitz, to name just a few. His accomplishments in industry are impressively broad: from co-designing the DEC Alpha Architecture to working on Adobe's Photoshop and speeding up Google web services such as Gmail.

When I met Dick (joining DEC in 1995), he was already a legend of our field, and I had the unique pleasure of spending time with him during his Google tenure and witnessed his problem-solving approach firsthand. Readers of this book will delight in the clarity of Dick's writing and how performance debugging problems are described as mysteries to be solved through his knowledge of hardware/software interactions and sequences of clues unveiled by observing detailed traces of program execution. This is a book that will be immensely useful for programmers and computer designers alike, in no small part because there is no other book to compare it with. It is as unique as its author.

—Luiz André Barroso, Google Fellow

#### **Preface**

Understanding the performance of complex software is difficult. It is even more difficult when that software is time-constrained and mysteriously exceeds its constraints now and then. Software professionals have pictures in their heads of their software's *execution dynamics*: How the various pieces work and interact together over time and estimates of how long each piece takes. (Sometimes they even document those pictures.) But when time constraints are not met, we have few tools for understanding *why*—for finding the root cause(s) of delay and other performance anomalies. This is a textbook for software developers and advanced students who work on such software.

Software dynamics refers not just to the performance or execution time of a single program thread but to the interactions between threads, between unrelated programs, and between an operating system and user programs. Delays in complex software often are caused by these interactions—code blocking and waiting for other code to wake it up, runnable code waiting for the scheduler to assign it a CPU to run on, code running slowly due to shared-hardware interference from other code, code not running at all because an interrupt routine is using its CPU, code invisibly spending much of its time in operating-system services or in page-fault handling, code waiting for I/O devices or network messages from other computers, and so on.

*Time-constrained* software handles repeated tasks that have periodic deadlines or tasks that have an aperiodic arrival rate of new requests each with a deadline. These tasks can have *hard* deadlines for sending control signals to moving machinery (airplanes, cars, industrial robots), *soft* deadlines such as for converting speech to text on the fly, or just *aspirational* deadlines such as for customer database lookup or web-search response times. Time-constrained also applies to phone/tablet/desktop/game user-interface responses. The term *time-constrained* is broader than the term *real-time*, which often implies hard constraints.

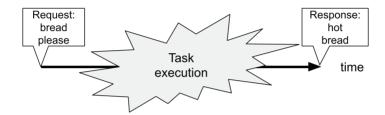

In each case, software tasks have a stimulus or request and a result or response. The elapsed time between the stimulus and result, the *latency* or *response time*, has some deadline. Tasks that exceed their deadlines fail, sometimes in catastrophic ways and sometimes in merely frustrating ways. You will learn how to find the root causes for these failures.

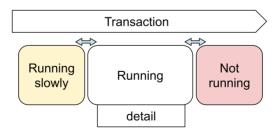

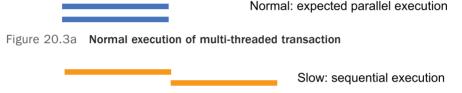

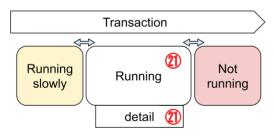

The individual tasks within such software can be called *transactions*, *queries*, *control-responses*, or *game-reactions* depending on the context. Here we will use the term *transactions* to encompass all of these. Often an end-to-end task is composed of several sub-tasks, some of which run in parallel and some of which depend on the completion of other subtasks. Sub-tasks may be CPU-bound, memory-bound, disk-bound, or network-bound. They may be executing but more slowly than expected due to interference across shared hardware resources or due to power-saving strategies in modern CPU chips. They may be waiting (i.e., not executing) for software locks or for responses from other tasks or other computers or external devices. There may be unexpected delays or interference from the underlying operating system or its kernel-mode device drivers, rather than in the programmer's user-mode code.

In many situations the software involved consists of a dozen or more *layers* or subsystems, all of which may contribute to unexpected delays and all of which may be running on separate networked computers. For example, a Google web search may spread the query across 2,000 computers, each of which does a small portion of the search and then the results are passed back and prioritized. An email message arrival in the cloud may trigger subsystems for databases, network

disk storage, indexing, locking, encryption, replication, and cross-continent transmission. An automobile-driving computer may be running 50 different programs, some of which interact on every video frame coming from a half-dozen cameras, plus radar returns, changing GPS coordinates, changing 3D acceleration forces on the vehicle, and feedback about rain, visibility, tire slippage, etc. A small database system might have query optimization and disk-access subsystems using a dozen disks spread across several networked computers. A game can have subsystems for local computation, graphics processing, and networked interactions with other players.

You will learn in this book how to design in observability, logging, and timestamps for such software, how to measure CPU/memory/disk/network behavior, how to design low-overhead observation tools, and how to reason about the resulting performance data. Once you have an accurate picture of the actual elapsed-time tasks and sub-tasks for normal transactions and also for slow ones, you can see how that reality differs from the picture in your head. At that point, substantially improving the slow transactions may take only 20 minutes of software changes. But without a good picture of reality, programmers are reduced to guessing and "trying things" to reduce long delays and improve performance. This book is about not guessing, but knowing.

All of the examples, programming exercises, and supplied software in this book are written in C or C++, based on the Linux operating system running on 64-bit AMD, ARM, or Intel processors. The reader is assumed to be familiar with developing software in this environment. We assume further that the reader has some software that is time-constrained and has performance issues that the reader wants to fix. The software should already be functional and deemed debugged, with acceptable average performance—the problem is just unexplained performance variance. The reader is assumed to have an in-the-head picture of how the software runs and can on request sketch how the pieces are *supposed* to interact in a typical transaction. Finally, the reader is assumed to know a little about CPUs, virtual memory, disk and network I/O, software locks, multi-core execution, and parallel processing. Together, we will take it from there.

We explore three major themes: Measure, Observe, and Reason.

**Measure**. The starting place for any performance study is to measure what is happening. A numerical measurement—transactions per second, 99th percentile response time, or dropped video frame count—tells you only what is happening but not why.

**Observe**. To understand why some measurement is unexpectedly slow or otherwise bad but measuring the same work again is fast, it is necessary to observe in close detail where all the time is going or what processing is being done for both normal and slow instances. For the hard case of unexpectedly bad behavior that only occurs under heavy live load, it is necessary to observe over a substantial enough time interval to have a high probability of observing several slow instances and to do so in situ with minimal distortion while running full live loads.

Reason (and fix). Once careful observations are available, you need to reason about what you see—how are slow instances different from normal ones, how do software and hardware interactions produce slow instances, and how can you improve the situation? In the last part of the book, we go through case-study examples of such reasoning and some of the fixes.

Following these themes, the book material is organized into four parts, including a part about building the low-overhead KUtrace observation tool:

Part I (Chapters 1–7), Measurement—how to do careful measurements of the four fundamental computer resources: CPU, memory, disk/SSD, and network.

- Part II (Chapters 8-13), Observation—normal observation tools: logging, dashboards, counting/profiling/sampling, and tracing.

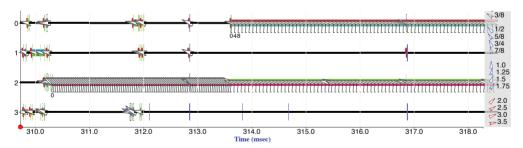

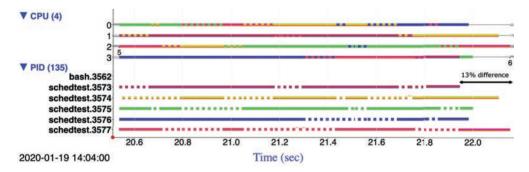

- Part III (Chapters 14–19), Kernel-User Trace—the design and construction of a running low-overhead Linux tracing tool that records what every CPU core is doing every nanosecond, along with postprocessing programs to create dynamic HTML pages that display the resulting timelines and interactions.

- Part IV (Chapters 20–30), Reasoning—case studies of reasoning about the interference underlying unusual delays observed in: excess execution, slow instruction execution, waiting for CPU, memory, disk, network, software locks, queues, and timers.

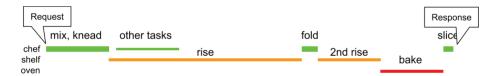

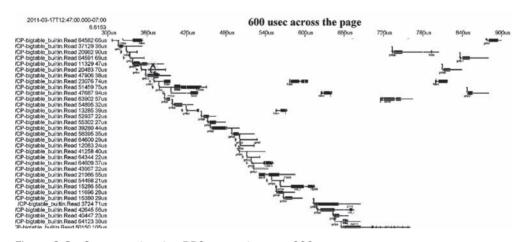

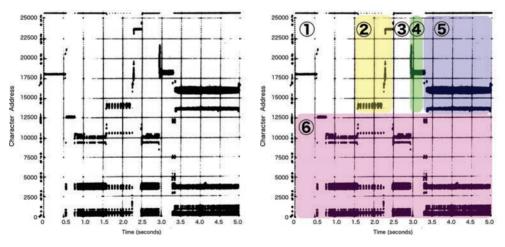

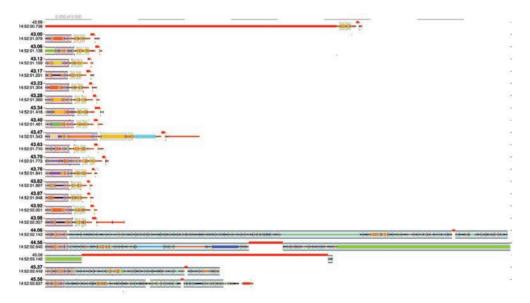

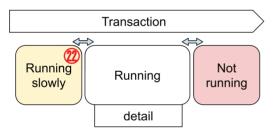

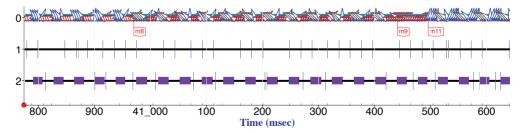

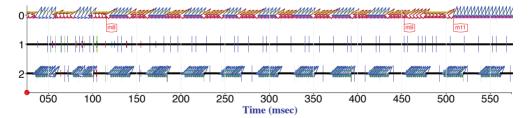

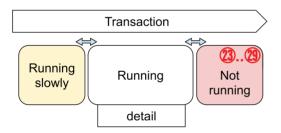

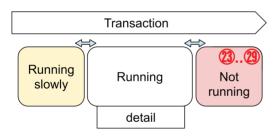

Using these ideas, you will be able to turn this picture of unexplained delay:

into the following detailed picture showing which subtasks happened when, which happened in parallel, which depended on another step finishing, and thus exactly *why* it took three hours:

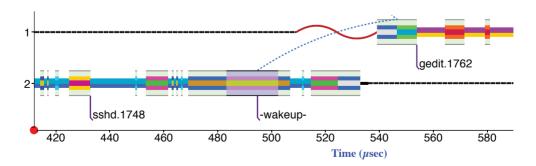

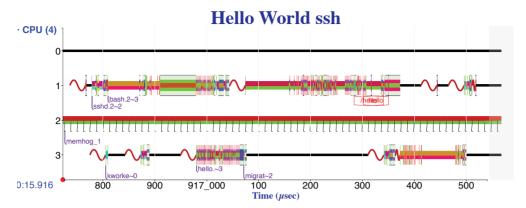

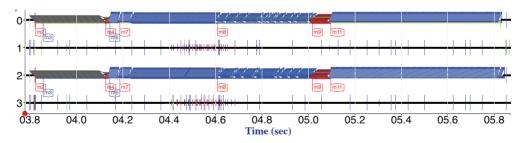

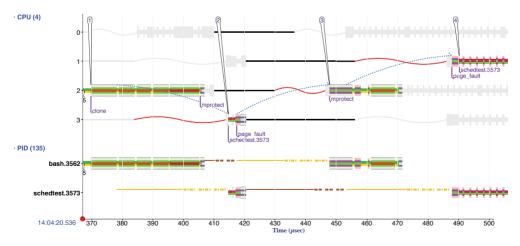

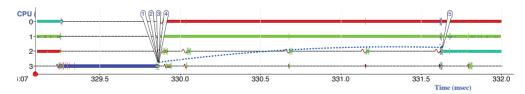

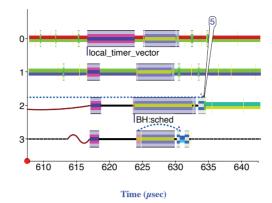

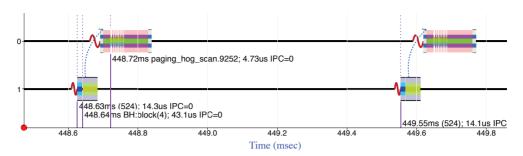

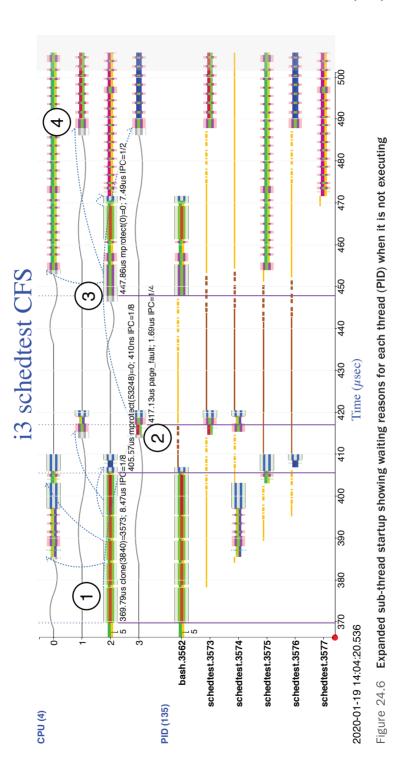

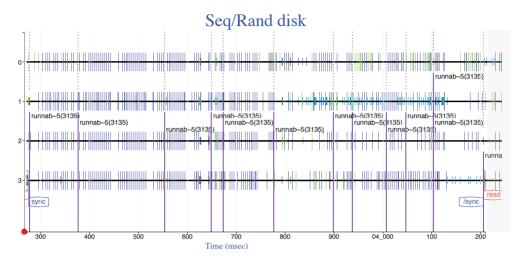

The same ideas can turn an example software delay into this picture of the remote-login ssh daemon on CPU 2 waking up gedit on CPU 1:

(In Part III you will learn how to create this last kind of picture for your arbitrary software.)

This book is intended especially for engaged readers who do the included programming assignments and who implement portions of the software observation tools described.

Layered throughout this book are comments about modern complex processor chips and their performance-enhancing mechanisms. Accidently defeating these mechanisms can create surprising delays. The careful reader will gain a deeper understanding of computer architecture and microarchitecture, along with everything else.

This is a textbook for software professionals and advanced students. But it also covers material of interest to computer hardware architects, operating system developers, system-architecture IT professionals, real-time system designers, and game developers. Its focus on understanding user-facing latency will develop skills that enhance any programmer's career.

### **Accessing the Source Code**

The book uses several computer programs: mystery1, mystery2, and so forth. The source code for these programs is available for download from Addison-Wesley at informit.com/title/9780137589739.

Register your copy of *Understanding Software Dynamics* on the InformIT site for convenient access to updates and/or corrections as they become available. To start the registration process, go to informit.com/register and log in or create an account. Enter the product ISBN (9780137589739) and click Submit. Look on the Registered Products tab for an Access Bonus Content link next to this product, and follow that link to access any available bonus materials. If you would like to be notified of exclusive offers on new editions and updates, please check the box to receive email from us.

# **Acknowledgments**

Many people have helped along the path to this book. Amer Diwan, V. Bruce Hunt, Richard Kaufmann, and Hal Murry have actively read and provided feedback on the text. Connor Sites-Bowen, J. Craig Mudge, Jim Maurer, and Rik Farrow provided thoughtful reviews and encouragement for earlier versions and related articles. Brian Kernighan did a thorough reading of the manuscript and made suggestions to materially improve the final product.

Much of the material here was developed from graduate courses I taught after retiring from Google in 2016. I am grateful for the opportunities and the student feedback arranged by Michael Brown at the National University of Singapore; Jim Larus and Willy Zwaenepoel at Ecole Polytechnique Federale de Lausanne; Christos Kozyrakis at Stanford University; and Kevin Jeffay and Fred Brooks at the University of North Carolina.

Joshua Bakita, Drew Gallatin, and Hal Murray have done ports of KUtrace to different Unix flavors. Jim Keller and Pete Bannon provided me the opportunity to do a port at Tesla Motors. Sandhya Dwarkadas asked the key question about detecting cache interference that led to my adding instructions-per-cycle counting to KUtrace.

My early career became focused on CPU performance and tracing through the influence and guidance of Elaine Bond, Pat Goldberg, Ray Hedberg, Fran Allen, and John Cocke at IBM; Don Knuth at Stanford; and Joel Emer, Anita Borg, and Sharon Perl at Digital Equipment Corporation.

My wife of 37 years, Lucey Bowen, has been especially gracious and supportive while I spent too much time focused on completing the book.

My editor, Greg Doench, has been particularly helpful in bringing this project to a smooth completion. He took time in the early months to arrange trial runs of importing text and the extensive figures into the publishing workflow, saving time and grief near the end of the process. My copy editor, Kim Wimpsett, did a fantastic job inserting literally thousands of small improvements.

—Richard L. Sites, September 2021

## **About the Author**

**Richard L. Sites** wrote his first computer program in 1959 and has spent most of his career at the boundary between hardware and software, with a particular interest in CPU/software performance interactions. His past work includes VAX microcode, DEC Alpha co-architect, and inventing the performance counters found in nearly all processors today. He has done low-overhead microcode and software tracing at DEC, Adobe, Google, and Tesla. Dr. Sites earned his PhD at Stanford in 1974; he holds 66 patents and is a member of the US National Academy of Engineering.

# Part I

# Measurement

Understanding variation is the key to success in quality and business.

—W. Edwards Deming

Measurement is the act of ascertaining the size, amount, or degree of something. Careful measurements are the underpinning of understanding software performance.

This first part describes a complex hardware and software environment, the book's emphasis on transaction latency, the concept of latency distributions, and the consequences of long 99th percentile latencies.

Our overall goal is to understand the root causes of *variance* in transaction latency—the apparently random unexpectedly long response times in complex software.

The datacenter environment is a superset of the environment you might have set up when exploring the performance of database transactions, desktop software delays, dedicated controller delays, or game delays. This part also introduces the important practice of estimating within a factor of 10 how long pieces of code should take. As an underpinning for the rest of the book, it leads readers through detailed measurements of CPU, memory, disk, and network latencies. These chapters use pre-supplied but flawed programs that every reader can run and get some insight and then can modify as directed to fix the flaws and gain substantially more insight. The resulting measurements will start to show the sources of latency variation in simple programs.

The first part serves to bring readers with varying backgrounds to a common base of knowledge about performance measurement, user- and kernel-mode software interactions, cross-thread and cross-program software interference, and interactions between complex software and computer hardware. At the end of this part, every reader will be able to make informed estimates of how long a piece of code *should* take.

# Chapter 1

# My Program Is Too Slow

Someone walks into my office and says "My program is too slow." After a pause, I ask "How slow should it be?"

A good programmer has a ready answer to this question, as she describes the work to be done and estimates of how long each portion should take. Perhaps she says "This database query accesses 10,000 records of which about 1,000 turn out to be relevant; each access should take about 10 milliseconds and they are spread across 20 disks, so 10,000 accesses should be about 5 seconds total. There is no network activity and the CPU processing and memory use are small and simple—all much faster than the disk access time. The actual query is taking about 15 seconds, which is too slow."

A sloppier programmer might answer "I wrote 1,000 lines of code all night using lots of existing libraries, and it all works but takes about 15 seconds per query, and I want it to take 1/10 of a second. One of those libraries must be too slow; how can I find it?" When asked, he has no idea whether 1/10 of a second is a reasonable expectation, no idea how long each library call should take, no idea if he is using the libraries appropriately, and no designed-in way to observe the dynamics of his code to determine where the time really goes. We will explore all these issues in this book.

#### 1.1 Datacenter Context

We introduce some terms and concepts from a complex software environment. Your environment may be much simpler, but the ideas carry over almost exactly. The terminology is from datacenters, but the ideas also apply to database, desktop, vehicle, gaming, and other time-constrained environments.

A *transaction* or *query* or *request* is an input message to a computer system that must be dealt with as a single unit of work. Each computer processing transactions is termed a *server*. The *latency* or *response time* of a transaction is the time elapsed between sending a message and receiving its result. The *offered load* is the number of transactions sent per second; when this exceeds the number of transactions processed per second, response time suffers, sometimes dramatically. A *service* is a collection of programs that handle one particular kind of transaction. Large datacenters process transactions for dozens of different services simultaneously, and each service has a different offered load and a different latency goal.

#### 4 Chapter 1 My Program Is Too Slow

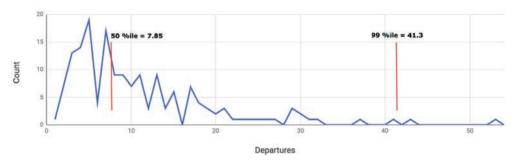

Transaction latency is not constant—it has a probability distribution taken over thousands of transactions per second. *Tail latency* refers to the slowest transactions in this distribution. A simple way to summarize the tail latency is to state the 99th percentile latency—the time that is exceeded by the slowest 1% of all transactions, i.e., by 50 transactions every second if the offered load is 5,000 transactions per second.

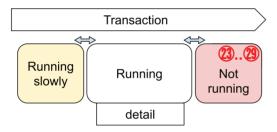

By the *dynamics* of a program or collection of programs we mean the activity over time—what pieces of code run when, what they wait for, what memory space they take, and how different programs affect each other. As programmers, we imagine in our heads simple dynamics for a program, but in reality the program may (occasionally) behave much differently than that picture and perform much more slowly than expected. If we can observe the true dynamics, we can adjust our mental picture and usually improve the code's performance with simple changes.

We are interested in user-facing transactions in complex software—the datacenter half of cell phones, for example. We are particularly interested in transactions that are usually fast but occasionally take much longer—enough that the end user sees an annoying delay. In datacenters, the hardware budget for each service is often determined by how many transactions per second each server can "handle." This target number is determined *empirically* by increasing the offered load until some tail-latency time constraint is exceeded, and then the target load is backed off a little.

If we can understand and then reduce the number of too-long transactions, the same hardware can handle larger loads within the tail-latency goal, at no additional cost. This is worth a lot of money. A skilled and somewhat lucky performance engineer can occasionally make a simple software change that saves enough money to pay for 10 years of salary. Companies and customers like such people.

Time-constrained transaction software is fundamentally different from batch or offline software (or most benchmarks). The important metric for transaction software is response time, while the important metric for batch software is usually efficient hardware utilization. For transactions, it is not the *average* response time that matters, but the slowest times, the tail latency.

In a datacenter, a higher average latency but shorter tail latency is usually preferred over a lower average latency and longer tail latency. Most commuters prefer the same thing—a route that takes a few minutes longer but always takes about the same time is better than a slightly faster route that occasionally has unpredictable hour-long delays.

For batch software, having the CPUs 98% busy on average can be good; for transaction software, 98% busy is a *disaster*, and even CPUs 50% busy on average might be too much, because it produces long response times whenever the offered load spikes for a few seconds to 3x above the average. When I first joined Google in 2004, the average datacenter CPU was 9% busy and 91% idle. The 9% busy was too low. Increasing that to 18% without increasing tail latency doubled the efficiency of all those datacenters. Doubling again to 36% busy would be good, but doubling a third time to 72% busy would likely ruin too many transactions' time constraints.

In looking at the performance of complex transaction-oriented software, we assume in this book that the programs involved fundamentally work and that on average they work quickly enough.

We won't discuss designing or debugging such software, nor understanding or improving its average performance. We also assume that always-slow transactions have been identified and fixed in offline test/debug environments that have no time constraints, leaving us just with occasionally slow transactions. We focus on the mechanisms that make occasional transactions slow, on how to observe these mechanisms, and on how to interpret the observations.

When you use a cell phone to send a text message, read a post, search the web, look at a map, stream a video, use an app, or even dial a telephone number, there is a datacenter somewhere that responds to your requests. If these responses are annoyingly slow and some competing app or service is faster, you may well switch to that one, or at least use the slow one less often. Everyone in a time-constrained ecosystem has an incentive, often financial, to reduce annoying delays. Few people have the skills to do so.

It is the goal of this book to teach a few more people how.

#### 1.2 Datacenter Hardware

Large datacenters have something like 10,000 servers in a building, with each server a PC about the size of a desktop PC but without the case. Instead, about 50 server boards are mounted in a rack, and there are 200 racks spread around a very large room. A typical server has 1–4 CPU chip sockets with 4–50 CPU cores each, a boatload of RAM, a couple of disks or *solid-state drives* (SSDs), and a network connection to a datacenter-wide switching fabric set up so that any server can communicate with any other server, and at least some of the servers can also communicate with the Internet and hence your phone. Outside the building, there are big generators that can run the entire building, including air conditioning, for days or weeks when there is a power outage. Inside, there are batteries that can run the servers and network switches for tens of seconds while the generators start up.

Each server runs multiple programs. It usually doesn't make business sense to dedicate some servers to just doing email, others to just map tiles, and others to just instant messages. Instead, each server runs multiple programs, and each of those programs likely has multiple *threads*. For example, an email server program might have 100 worker threads processing email requests for several thousand users simultaneously, most of whom are typing or reading, with many of the active threads waiting for disk accesses or for other software layers. The worker threads take incoming requests, do whatever is asked, respond, and then go on to another pending request from another user. During the busiest hour of the day almost all the worker threads are busy, while during the slowest hour of the day at least half of them will be idle, waiting for work. There is a constant boom-and-bust cycle of offered work at almost all time scales—microsecond, millisecond, second, and minute. There is even a seven-day cycle with lower activity on Saturday and Sunday (for Western work weeks).

To control response times, it is important to have spare hardware resources available for user-facing transactions, since the user load tends to spike now and then based on physical-world events. But it is also economical to have some non-user-facing batch programs to run when there are otherwise idle processors. In addition to user-facing foreground programs and batch

<sup>&</sup>lt;sup>1</sup>A computer science technical term, 10<sup>12</sup>

background programs, there are always a few supervisory programs running on each server, keeping track of how busy that server is, how many errors it is getting, how much disk space is left, etc. These supervisory programs deal with machine health and rebooting/reconfiguring individual machines and with starting/stopping /restarting the various software programs. It turns out to be a complex environment just on a single server. This complexity is then multiplied by 10,000 for a roomful of servers.

#### 1.3 Datacenter Software

Datacenter software is quite different from self-contained programs and benchmarks. It consists of *layers and layers* of subsystems, many running in parallel, each handling requests from multiple services and multiple instances of single services, and each trying to respond quickly enough to each request to meet its individual latency goals. Often, the layers serving one user request will all be running on different servers. To improve performance, many layers will include software caches holding recent data or calculated results. Finding and reusing software-cached data is termed a *hit* and not finding it a *miss*. The dynamics of software caches can affect transaction latency in unexpected ways, as we shall see.

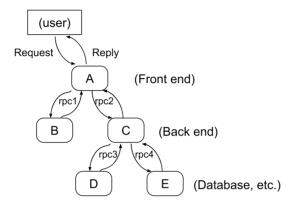

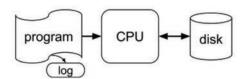

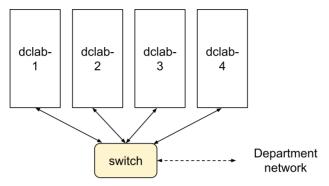

A user requesting the text of an email message would first have that request routed to a data-center containing the primary mail repository for that user and then go through a load-balancing server that forwards the request to a less busy one of hundreds of email front-end servers. The front-end software layer manages the request and eventually constructs the HTML or app API result. It requests the mail message itself from a back-end layer, which calls a *database layer*, which calls a database caching layer and upon software-cache miss calls a replication layer (to access or update a secondary mail repository in another datacenter), and eventually there is a call to a disk-server layer that reads the mail message from one of several redundant disks, as shown in Figure 1.1. Results are then returned up the call tree, possibly being modified as they go.

Figure 1.1 Layers of a software example

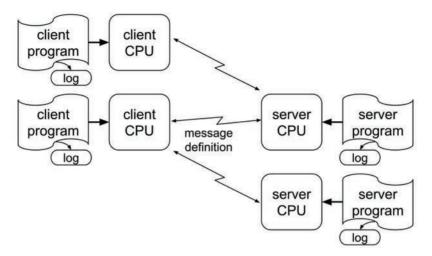

Some form of network message passing or remote procedure call ties all this activity together. We will use the term *remote procedure call* and its abbreviation RPC throughout this book. RPCs from one layer to another may be synchronous, with the caller waiting for a response, or asynchronous with the caller continuing to execute and quite possibly doing other RPCs that all execute in parallel on many different servers. It is this parallel execution of small portions of work that allows datacenter software to perform massive amounts of work for one request and

still finish in a fraction of a second. A single user-facing transaction may easily fan out to use 200–2,000 different servers.

Figure 1.2 shows a small example RPC tree, in the style of [Sigelman 2010]. Server A might call B synchronously and then after B returns call C. Server C might call D and E in parallel and then wait for both to return.

Figure 1.2 RPC tree across five servers A-E

Each user request and each RPC sub-request has a response-time goal. If the user request at an email front-end layer has a 200-millisecond goal, the back-end layer might be given a 160-millisecond goal, the database layer a shorter goal, and so on down to a disk-server goal of 50 milliseconds. Whenever a sub-request responds too slowly, each of the layered callers is also exposed to responding too slowly. For a set of parallel executions, the term *execution skew* describes the variation in completion times.

If many RPCs are done in parallel, it is usually the slowest of these that determines the overall response time. Thus, if we execute 100 RPCs in parallel, it is the 99th percentile slowest response time that sets the overall response time. Execution skew makes understanding and controlling long response times important.

#### 1.4 Long-Tail Latency

Latency is the elapsed wall-clock time between two events. When carefully discussing latency, be sure to specify which two events. For example, "the latency of an RPC" might mean the time between a user-mode program (client in client-server terminology) sending a request and that program receiving the corresponding response. Or it might mean the time from when the called user-mode program (server in client-server terminology) receives a request to when it sends the corresponding response. These two different definitions of latency, client and server, may sometimes differ by 30 milliseconds or more for the same RPC, with some mystery involved about where the extra time goes and on which computer or network hardware.

We will focus by default on *server* RPC latency except when we are discussing discrepancies such as the 30 milliseconds earlier.

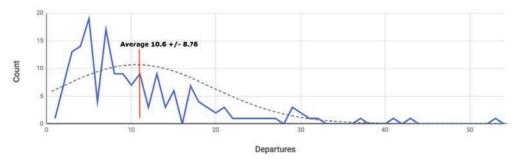

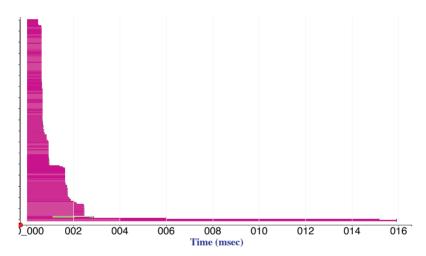

Multiple RPC requests to a service will have different latencies, but they often will cluster near similar values for similar requests. In general, this can be summarized by a histogram of latency values—a little graph showing latency buckets on the x-axis and count of RPCs with that latency on the y-axis.

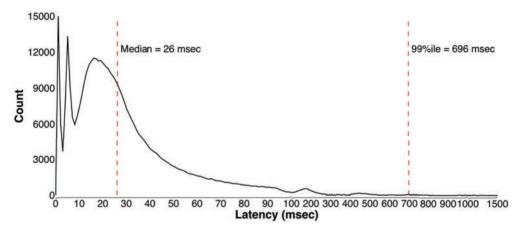

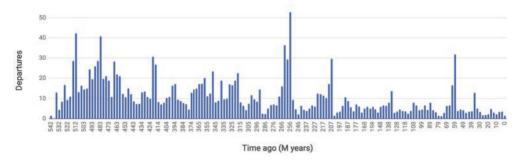

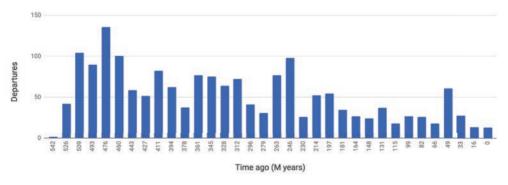

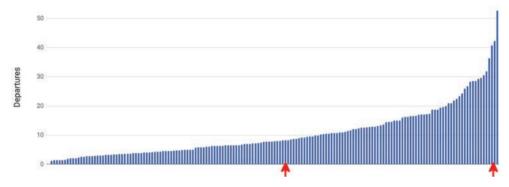

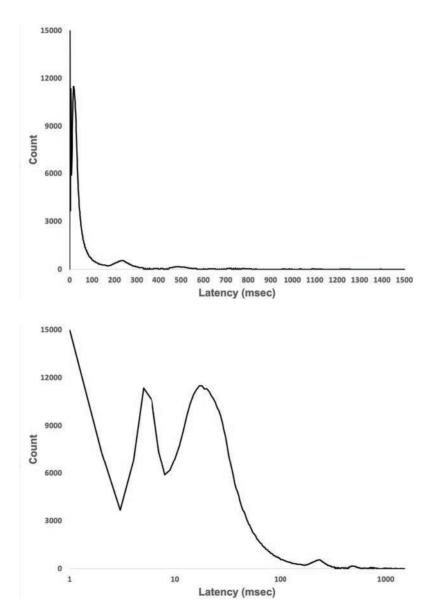

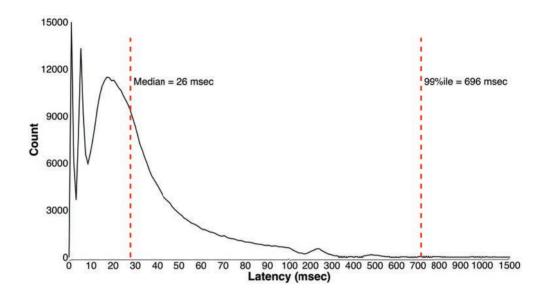

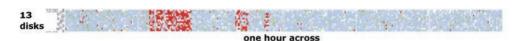

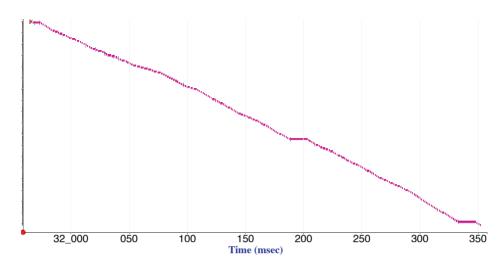

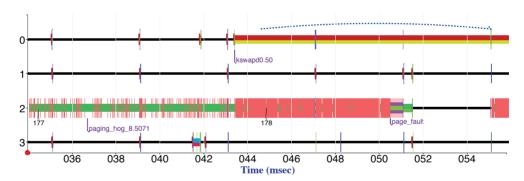

For datacenter transactions, these latency histograms have one or more peaks for normal cases but often have a *long tail* of substantially slower responses for unusual cases [Blake 2015, Hoff 2012, Weaveworks 2017, Dean 2013]. The disk-server histogram in Figure 1.3 has three peaks at about 1, 3, and 20 milliseconds for three different kinds of normal cases, and then a long tail that extends out beyond 1,500 milliseconds. The desired response time is 50 milliseconds or less. This book is about understanding and reducing the long tail. The barely visible peaks soon before 250, 500, 750, etc., milliseconds are indications of an underlying performance mystery, which we will resolve in Part II.

Figure 1.3 Histogram of disk-server accesses with long tail on the right

It is useful to describe a latency histogram with just a few numbers, instead of 500 numbers if the histogram has 500 buckets. What number should we use?

The median (or similar average) latency is a particularly ill-suited description of a skewed or multipeak distribution because it rarely is near many of the actual values and it tells us nothing about the shape and size of the long tail—our topic of interest. In the graph in Figure 1.3 the median latency is 26 milliseconds, telling us nothing about the peaks or the tail. The maximum latency is also ill-suited because there might be one extremely slow RPC in a day (associated with a recovered memory or disk hardware error, for example) and all the others are tens to hundreds of times faster.

Instead we turn to percentiles. If our latency histogram has 50,000 measurements, then the shortest 500 of these are the fastest 1% and the longest 500 are the slowest 1%. The numeric boundary between the fastest 99% and slowest 1% is the 99th percentile value—99 percent of the sorted measurements are less than or equal to this value. (There are many such values, all lying between the 49,500th and 49,001st sorted measurements; any of these numbers will do, but conventionally the exact 49,500th sorted value will be used.) A quick but useful way

to describe a long-tail distribution is to give the 99th percentile value, or 95th, 99.9th, etc. The 99th percentile value for the histogram in Figure 1.3 is 696 milliseconds, which is much too large compared to the 50-millisecond goal. It represents a serious performance bug.

In Chapter 9, we will learn what caused this particular long tail, how it was fixed, and the eventual new 99th percentile of about 150 milliseconds. That simple change paid for 10 years of my salary.

# 1.5 Thought Framework

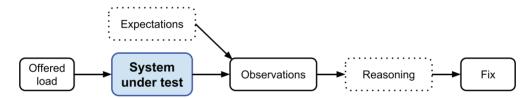

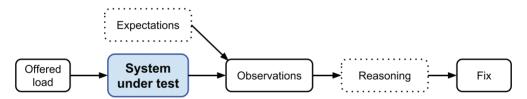

In thinking about tail latency and related performance issues, we will follow the programmer's discipline of first estimating how long some work should take, then observing how long it actually does take, and then thinking about any differences. Figure 1.4 shows this framework.

Figure 1.4 Framework for examining the performance of complex software

The framework consists of a software and hardware system under test, some offered load for that system, a human's expectations of the performance of the system for such a load, software performance-tool observations of the actual dynamics and performance, human reasoning about what is happening, and eventually fixes or changes to improve the performance.

# 1.6 Order-of-Magnitude Estimates

In looking at software performance, part of "How slow should it be?" is estimating how long various pieces of work should take. These estimates can be very rough and still give useful insight. Performance-aware programmers do order-of-magnitude estimates in their heads all the time while designing and writing serious programs.

The phrase *order of magnitude* refers to an approximate measure of the size of a number. A *decimal* order of magnitude gives an estimate that is the nearest power of 10 (1, 10, 100, ...), while a *binary* order of magnitude gives an estimate that is the nearest power of 2 (1, 2, 4, 8, and so on). Occasionally, you will see decimal half-orders—1, 3, 10, 30, etc. In this book, we use decimal orders of magnitude unless otherwise qualified, using the notation O(n) for "on the order of n," with the *units* always specified. It matters a lot whether you are talking about O(10) nanoseconds or O(10) milliseconds or O(10) bytes. From here on in the book, we will also use *nsec*, *usec*, and *msec* to abbreviate nanoseconds, microseconds, and milliseconds, respectively.

In Table 1.1 you will find a series of estimates that every serious programmer should be familiar with. It is from a 2009 talk by Jeff Dean, one of the very few Google Fellows. The numbers have not changed much since then. I have added a column of just order-of-magnitudes.

Table 1.1 Numbers Everyone Should Know [Dean 2009]

| Action                             | Time             | <b>O</b> (n) |

|------------------------------------|------------------|--------------|

| L1 cache reference                 | 0.5 nsec         | O(1) nsec    |

| Branch mispredict                  | 5 nsec           | O(10) nsec   |

| L2 cache reference                 | 7 nsec           | O(10) nsec   |

| Mutex lock/unlock                  | 25 nsec          | O(10) nsec   |

| Main memory reference              | 100 nsec         | O(100) nsec  |

| Compress 1K bytes with Zippy       | 3,000 nsec       | O(1) usec    |

| Send 2K bytes over 1 Gbps network  | 20,000 nsec      | O(10) usec   |

| Read 1 MB sequentially from memory | 250,000 nsec     | O(100) usec  |

| Round trip within same datacenter  | 500,000 nsec     | O(1) msec    |

| Disk seek                          | 10,000,000 nsec  | O(10) msec   |

| Read 1 MB sequentially from disk   | 20,000,000 nsec  | O(10) msec   |

| Send packet CA->Netherlands->CA    | 150,000,000 nsec | O(100) msec  |

Doing an order-of-magnitude estimate of expected times in various parts of a program makes it easy, when you get real measurements of those times, to spot ones that differ substantially from your expectations. **This is where the learning is.** Sometimes your estimate will be quite wrong and you get to learn something subtle about how computers or programs work. Sometimes your estimate will be about right but the program is doing something much different than the picture in your head, and that unexpected faster or slower behavior needs fixing. As you practice and get better at estimating, more and more of the discrepancies you find will be real performance bugs.

Knowing the estimates in Table 1.1 will also guide you in identifying the likely source of a performance bug. If some program fragment takes 100 msec more than you expect, the problem is unlikely to be related to branch misprediction, whose effect is 10,000,000 times smaller than 100 msec. It is more likely related to disk or network times, or as we will see in later chapters, to long lock-holding times or to waiting on long RPC sub-requests.

We will design and build observation tools and data displays. As you use them, get in the habit of predicting within an order of magnitude what you expect to see. Once you are practiced at this prediction-observation-comparison loop, you will rapidly start spotting the odd stuff.

# 1.7 Why Are Transactions Slow?

Recall that we are particularly interested in transactions that are usually fast but occasionally take a lot of extra time—enough that the end user sees an annoying delay. In particular, slow transactions are those that violate a written response-time goal. What can cause such delays; i.e., what can cause varying latency and especially long-tail latency?

The clue here is that a transaction or transaction type is usually fast. When it is slow, that indicates the normal transaction execution time plus some unknown delay. If we can identify the source of the delay, we can usually make simple code changes that remove most of that delay and thus shorten the long-tail latency.

In heavily layered software, the most common source of delay in one layer is that it is waiting for a response from a lower layer. The lowest slow layer could be slow for its own reasons, or it could be slow because it is swamped by *unreasonable offered load*. Be sure when you develop response-time goals to simultaneously develop offered-load goals, or more precisely *constraints*.

Changing one layer's code won't help if it is simply waiting on a lower layer. We need to find the lowest layer that is actually too slow and work on improving it. To do so, we will want to design in ways to observe how long each layer is taking and to turn those measurements into displays that make it quickly clear where the bottlenecks are. A simple such display shows the actual offered load vs. the offered-load goal and the actual response time vs. the response-time goal at each layer or each RPC interface.

If the offered load to a layer N is acceptable and that layer is not waiting excessively on a lower-level layer N+1 but layer N's response time is too slow, then we have RPCs to layer N running on a single server whose latency is often normal but occasionally is much longer. We want to observe that particular server in more detail. Either the slow RPCs are doing *extra work* that is not normally done or they are doing normal work but *executing slowly*—more slowly than usual.

Doing extra work is based on the branching structure of code and the state that it keeps. Programs vary enormously in how they can end up doing extra work, but they usually have the property that this extra work is done even if the program runs standalone on a server all by itself, with no other programs running. Such performance bugs are relatively easy to find by running the code offline in a test-bed environment, giving it clones or recordings of live traffic requests but running with extra instrumentation to find the errant branching pattern. Running on testing machines allows use of standard performance tools that slow down processing by 2x or even 20x or more. The book by Brendan Gregg [Gregg 2021] discusses many observation tools that are appropriately used in such an environment.

The more interesting case, and the subject of this book, is an RPC doing just the normal work but more slowly than usual. In other words, something is *interfering* with the RPC's normal work on a single server, slowing down its completion. We call these *hindered* transactions. Their delays usually do not occur in offline testing, but instead occur only when running a live user-facing load, often only during the busiest hour of the day. We want to find the source(s) of interference and remove or at least minimize them. Unfortunately, in this live environment, observation tools that slow down processing by 2x or even by 10% are too slow to be used. We need observation techniques and tools with less than 1% overhead if they are to be deployed in

live datacenters (or in vehicles or in heavy multiplayer gaming, etc.). There are very few of these available in our industry. Part III of this book introduces one.

Recall that in a datacenter environment, each server runs multiple programs, and each of those programs likely has multiple threads. Interference on a single server must come from something on that server (including incoming and outgoing network traffic). Interference in this environment comes almost exclusively from contention for a shared resource.

#### 1.8 The Five Fundamental Resources

There are only four computer hardware resources shared between unrelated programs running on a single server:

- CPU

- Memory

- Disk/SSD

- Network

If a program has multiple cooperating threads, there is a fifth fundamental resource:

Software critical section

A critical section is a piece of code that accesses shared data in a way that would not behave correctly if more than one thread does so concurrently. These code sections are protected by software locks so that only one thread at a time may execute them, with any other thread forced to wait to enter the critical section.

To spot interference you need an understanding of normal execution. The starting point is learning how to carefully measure each of the five fundamental resources. The remaining chapters of Part I cover the four hardware resources, but we defer covering software locks to Chapter 27, after we have developed an appropriate observation tool. If a slow RPC is trying to use any of these five resources and some other program or thread is also using it, our RPC will have to wait. This is the fundamental mechanism of interference or hindering.

# 1.9 Summary

This book is about understanding the dynamics of datacenter, database, desktop, gaming, and dedicated controller software transactions, especially ones that occasionally take much longer than usual. A good programmer can estimate within an order of magnitude how long any piece of code she writes should take and therefore can notice and fix code that is always too slow. We assume in this book that always-slow code has already been fixed. We are interested in the much harder to understand occasionally slow code.

On a datacenter server running thousands of transactions per second, some transactions will be slow occasionally and will be fast if run again. A histogram of transaction times will show a long tail of slow performers, and these will disproportionately affect the overall response times for users and will disproportionately reduce the amount of work a given server can do. These slow

transactions are suffering some form of interference, but with heavily layered datacenter software it is often difficult to determine which layer is actually slow for a particular transaction, and it is therefore difficult to know where to look for the interference.

Using order-of-magnitude estimates such as those in Table 1.1 can guide you in identifying likely sources or mechanisms for a performance bug, but usually cannot pin down the exact piece of slow code. For that, we will need to design in proper observation tools for layered software and for servers running many unrelated programs that can interfere with each other.

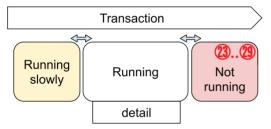

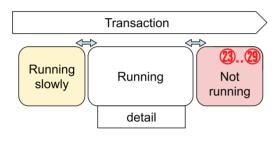

Overall, a transaction on a single server is either executing normally, executing slowly, or waiting for something on that server. The last two are caused by interference. We will explore the mechanisms for these last two and explore how to observe them *in situ*.

That's it. To solve occasionally slow transaction performance problems, all we have to do is (i) identify which layer of code is slow and then (ii) identify what is interfering with it and then (iii) fix that. The rest of this book is devoted to learning how to do these three simple steps. Unfortunately, the first two are hard.

- We focus on understanding occasionally slow RPC transactions.

- For 100 RPCs done in parallel, the 99th percentile slowest time sets the *overall* response time.

- Datacenter software is rife with execution skew—a long tail of substantially slower responses.

- Slower or hindered transactions mean that something is interfering with the RPC.

- Interference comes from sharing the five fundamental resources.

- Interference is hard to observe *in situ*; we will build some missing observation tools.

- Be sure to do order-of-magnitude estimates of expected times to more easily spot unexpected ones.

# Chapter 2

# **Measuring CPUs**

In this chapter and the following ones, you will learn how to measure each of the four fundamental hardware resources on x86 processors running Linux and using the gcc compiler, as described in Appendix A. The ideas here carry over to other processors and other software environments, but the numbers will vary somewhat.

Rather than encouraging you to just memorize Table 1.1 from Chapter 1, we will actively measure most of those values on computers you use. Along the way, you will learn the basics of designing measurements and also learn something about the subtleties of modern computers. When we are done, you will have a stronger underpinning for estimating how much time various pieces of code should take. These chapters also allow readers of varying backgrounds to fill in a few gaps in their knowledge of computers and software.

The first fundamental resource to measure is CPU time—how long real computer instructions take. A simple measurement of how long an add instruction takes is surprisingly subtle. What does "how long" mean in this context?

Modern CPUs can issue one or more instructions every CPU clock cycle, but an individual instruction may take several cycles to complete. If a particular type of instruction can issue every cycle but takes three cycles to produce a result that is available to a subsequent instruction, do we want "long" to mean one cycle or three cycles? Some instructions can take dozens of cycles, and these delay subsequent instructions that need their results. These delays may in fact be the performance problem we are trying to find. So we want "how long" to mean the *latency* of an instruction—the time in CPU clock cycles from issuing the instruction to a subsequent instruction being able to use its result.

If you are not very familiar with the terms *instruction fetch*, *pipelining*, *cache* memory, and (for the next chapter) *virtual memory*, now would be a good time to review a computer architecture textbook, such as Hennessy and Patterson [Hennessy 2017].

### 2.1 How We Got Here

In the golden age of computing, the 1950s, with CPU clock cycle and *core memory* (see the next chapter) cycle times being identical, simple instructions took two cycles to complete. Cycle 1 fetched and decoded the instruction word from memory, and cycle 2 accessed (read or write) a

data word in memory as part of the instruction execution, as shown in Figure 2.1a. A *word* on a popular machine of the time, the IBM 709 [Wikipedia 2020a], was 36 bits.

To speed things up, later machines such as the IBM 7094 II [Wikipedia 2021a] fetched an evenodd pair of instructions from memory at once, with the second held in a temporary instruction register while executing the first. The CPU then executed the second directly without another instruction fetch; thus, two simple instructions executed sequentially one at a time, but in three cycles instead of four, as shown in Figure 2.1b.

Another speedup technique had two or more independent core memory units, arranged so that the execution of instruction N could be overlapped with the fetch of instruction N+1 if they were accessing different memory units.

With the advent of transistors, CPU cycle times got faster, but core memory access times did not. To speed up processing, the CPU and memory clocks were decoupled, with the CPU running faster and each memory reference taking multiple CPU cycles. At the same time, more registers were added inside the CPU so that some instructions could do register-to-register operations that did not need to wait for a data access in memory, as shown in Figure 2.1c with a register write done in the last CPU cycle. Instructions with complex processing, such as multiply, could take several execution cycles before writing a result, as shown in Figure 2.1d.

| instruction fetch & decode execution |

|--------------------------------------|

|--------------------------------------|

Figure 2.1a Simple fetch/execute in two CPU cycles

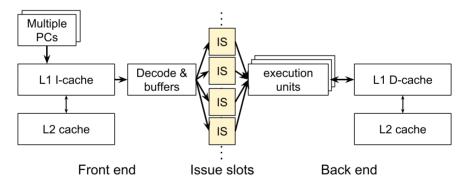

| instruction fetch & decode | execution |           |